SPP-IM977

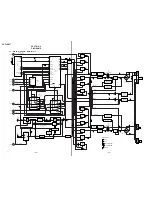

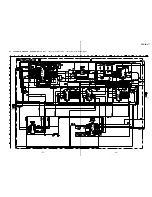

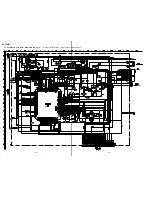

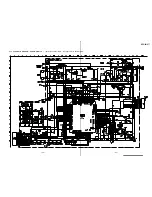

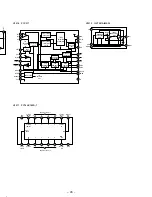

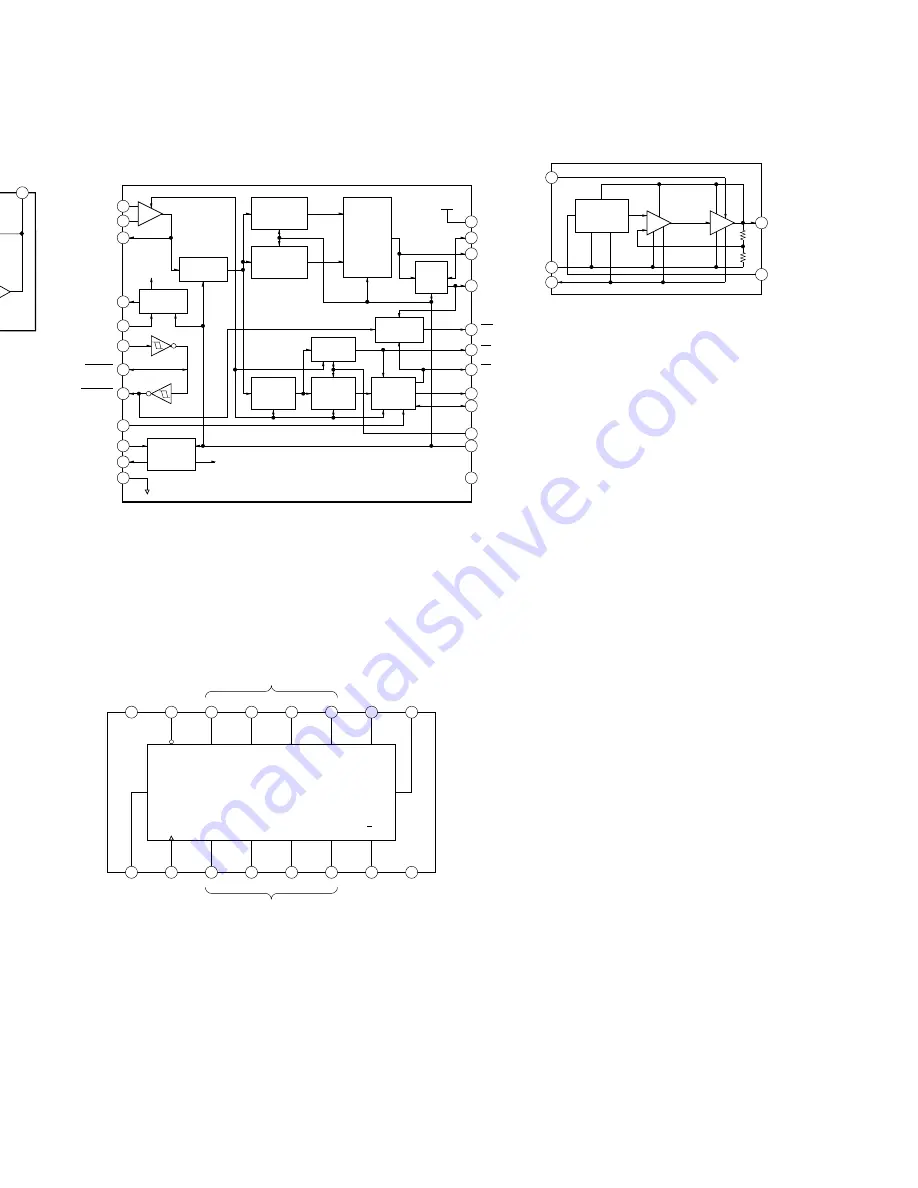

• IC Block Diagrams

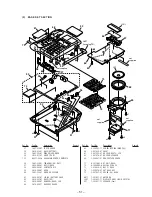

– BASE MAIN Board –

U1002, 1028

MC74HC4053DTR2

U1013

U4083B

+

8

7

6

5

4

3

2

1

_

+

_

VO2

CD

CF 2

CF 1

V in

GND

Vcc

VO1

BIAS

CIRCUIT

U1014

PCC317

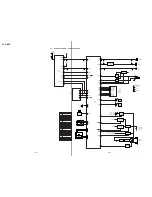

U1012, 1020, 1021

SN74HC595ADB-E05

U1017

PC74HC165D-T

– 47 –

– 48 –

16

15 14

13

12

11

10

9

1

2

3

4

5

6

7

8

C

B

A

OX

IX

X-COM

Y-COM

VCC

GND

VEE

INH

OZ

Z-COM

IZ

OY

IY

C

OUT

IN

C

OUT

IN

C

OUT

IN

C

OUT

IN

C

OUT

IN

C

OUT

IN

LOGIC LEVEL CONVERTOR

1

2

3

4

5

6

7

8

9

10

16

15

14

13

12

11

SHIFT REGISTER

LATCH

PARALLEL DATA

OUTPUT

GND

VCC

LATCH

CLOCK

PARALLEL DATA

OUTPUT

SERIAL DATA

INPUT

OUTPUT

ENABLE

SHIFT

CLOCK

SERIAL DATA

OUTPUT

RESET

QB

QC

QD

QE

QF

QG

QH

SQH

A

QA

1

2

3

4

5

6

7

8

9

10

16

15

14

13

12

11

CK

E

F

G

H

QH

D

C

B

A

SERIAL

IN

CLOCK

INHIBIT

SHIFT/

LOAD

GND

QH

VCC

OUTPUT

QH

SERIAL

INPUT

A

B

C

D

CLOCK

INHIBIT

SHIFT/

LOAD

CLOCK

E

F

G

H

OUTPUT

QH

PARALLEL INPUTS

PARALLEL INPUTS

3

4

5

6

7

8

9

10

16

15

14

13

12

11

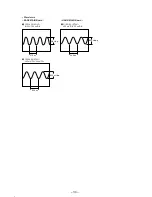

+

–

BIAS

GENERATOR

ANTI-ALIAS

FILTER

OSCILLATOR

ALERT SIGNAL

HIGH TONE

FILTER

ALERT SIGNAL

LOW TONE

FILTER

TONE

DETECTION

ALGORITHM

GUARD

TIME

INTERRUPT

GENERATOR

CARRIER

DETECTOR

FSK

DEMODUL-

ATOR

FSK

BANDPASS

FILTER

DATA

TIMING

RECOVERY

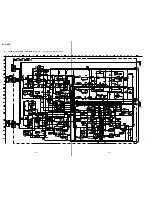

24

23

22

21

20

19

18

17

1

2

IN+

IN–

GS

VREF

CAP

TRIGIN

TRIGRC

TRIGOUT

MODE

OSCIN

OSCOUT

VSS

IC

PWDN

FSKEN

DCLK

DATA

DR

CD

INT

STD

EST

ST/GT

VDD

TO

INTERNAL

CCL

TO

INTERNAL

CCL

U1015

ILC7081AIM5-30

5

1

2

3

BANDGAP

REFERENCE

VREF

ERROR

AMP

TRANS-

CONDUCTANCE

AMP

VIN

GND

ON/OFF

4

VOUT

CNOISE

Summary of Contents for SPP-IM977

Page 26: ...SPP IM977 ...

Page 36: ......