STR-DA333ES/DA555ES

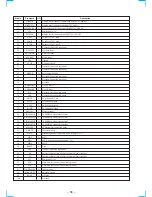

5-25. IC BLOCK DIAGRAMS

IC1101 CXD8495AQ (DIGITAL BOARD)

TIMING

GENERATOR

37

38

39

40

41

42

43

44

45

46

47

48

24

23

22

21

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

9

10

11

12

35

36

34

33

32

31

30

29

28

27

26

25

X' TAL

OSC

MUTING

OUTPUT

ERROR LOCK

DETECTION

DATA

DEMODULATOR

MICRO COMPUTER

INTERFACE

MULTI PLEXER

TEST

PLL CIRCUIT

CD SUB-CODE

DETECTION

LD/DQSY

SRDT

D0

DI/SWDT

CE/XLAT

CL/SCLK

D VDD

DIN1

DIN2

DIN3

DIN4

DGND

D GND

SBCK

SFSY

PW

SBSY

D VDD

VCO

V IN

A GND

R

A VDD

N.C.

LRCK

DATA OU

T

BCLK

SUB 2

SUB 1

D GND

ERROR

CLK OUT2

CLK OUT1

X OUT

X IN

D VDD

DOUT/V

EMPHA

RC1

RC2

CCB/SUB

D GND

CLKMD

CLK

TEST1

TEST2

X MODE

D VDD

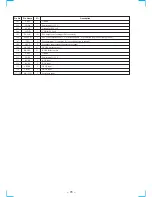

IC1106 CS4926 (DIGITAL BOARD)

DATA0,EMAD0,GPIO0

DATA1,EMAD1,GPIO1

DATA2,EMAD2,GPIO2

DATA3,EMAD3,GPIO3

DATA4,EMAD4,GPIO4

DATA5,EMAD5,GPIO5

DATA6,EMAD6,GPIO6

DATA7,EMAD7,GPIO7

VSS2

VDD2

A0,SCCLK

WR,

DS,

EMWR,

GPIO10

MCLK

CLK IN

XMT958

EXTMEM,

GPIO8

PARALLEL

or

SERIAL

HOST

INTERFACE

COMPRESSED

DATA INPUT

INTERFACE

SP DIF

RECEIVER

DIGITAL

AUDIO

INPUT

INTERFACE

PLL

CLOCK

MANAGER

RAM

INPUT BUFFER

RAM

OUTPUT BUFFER

OUTPUT

FORMATTER

30

CMPREQ,LRCKN2

29

CLKSEL

31

FILTD

32

FILTS

33

VDDA

34

VSSA

35

RESET

36

DD

37

DC

38

21

ABOOT

,

INTREQ

20

SCDIO,

SCDOUT

,

PSEL,

GPIO9

19

CMPCLK,

SCLKN2

28

CMPDA

T,

RCV958,

SDA

TAN2

27

LRCKN1

26

SCLKN1,

STCCLK2

25

VSS3

24

VDD3

23

SDA

TAN1

22

CS

18

7

44

SCLK

43

LRCLK

42

AUDA

TA

0

41

AUDA

TA

1

40

AUDA

TA

2

39

4

RD,

R/W

,

EMOE,

GPIO11

5

A1,

SCDIN

6

3

FRAMER SHIFTER

INPUT BUFFER CONTROLLER

17

16

15

14

13

12

11

10

9

8

VSS1

2

VDD1

1

RAM

PROGRAM MEMORY

RAM

DATA MEMORY

ROM

PROGRAM MEMORY

ROM

DATA MEMORY

24-Bit

DSP

PROCESSING

STC

IC1109 TC74VHC393FT(EL) (DIGITAL BOARD)

14

13

12

11

10

9

8

1

2

3

4

5

6

7

Q

A

Q

B

Q

C

Q

D

A

CLEAR

VCC

Q

A

Q

B

Q

C

Q

D

A

CLEAR

GND

IC1202 AK4324-VF-E2 (DIGITAL BOARD)

IC3310 TC74HC151AF (DIGITAL BOARD)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

D3

D2

D1

D0

Y

W

S

C

D4

D5

D6

D7

A

B

D3

D2

D1

D0

Y

XY

OE

GND

VCC

D4

D5

D6

D7

A

B

C

IC1210 AK5352-VF-E2 (DIGITAL BOARD)

18

23

15

17

22

24

13

12

4

5

19

20

21

8

10

11

14

SCLK

SMODE1

SMODE2

MCLK

CMODE

VB

DGND

VD

VA

AGND

VREF

AINL+

AINL–

AINR+

AINR–

LRCK

FSYNC

SDATA

TST1

9

HPFE

16

PD

TST2

TST3

TST4

Clock Divider

Voltage

Reference

Modulator

Serial Output

Interface

Digital Decimation

Filter

3

6

7

1

2

Modulator

DVSS

DVDD

PD

SMUTE

DFS

DEM0

DEM1

1

2

CKS

MCLK

3

4

5

BICK

SDATA

LRCK

6

7

8

9

10

11

12

DIF2

DIF1

DIF0

13

14

15

AVSS

VREF

AVDD

DZFR

DZFL

20

21

22

23

24

AOUTL–

AOUTL+

18

19

SCF

∆∑

MODULATOR

8x

INTERPOLATOR

AOUTR–

AOUTR+

16

17

SCF

∆∑

MODULATOR

8x

INTERPOLATOR

SERIAL INPUT

INTERFACE

CLOCK

DIVIDER

DEEMPHASIS

CONTROL

– 59 –

– 60 –

Summary of Contents for STR-DA333ES - Fm Stereo/fm-am Receiver

Page 2: ... 2 ...

Page 6: ... 6 SECTION 2 GENERAL This section is extracted from STR DA555ES instruction manual ...

Page 7: ... 7 ...

Page 8: ... 8 ...