STR-DN1050

86

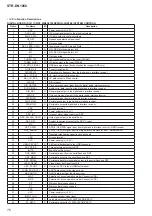

Pin No.

Pin Name

I/O

Description

AA4

DDR_/DQS[2]

O

Data strobe signal output to the SD-RAM

AA5

DDR_DQ[26]

I/O

Two-way data bus with the SD-RAM

AA6

DVDD_DDR

-

Power supply terminal (+1.8V)

AA7

DDR_/DQS[3]

O

Data strobe signal output to the SD-RAM

AA8

DDR_A[13]

O

Address signal output terminal Not used

AA9

DDR_A[8]

O

Address signal output to the SD-RAM

AA10

DVDD_DDR

-

Power supply terminal (+1.8V)

AA11

DDR_A[2]

O

Address signal output to the SD-RAM

AA12

GND

-

Ground terminal

AA13

DDR_/CS

O

Chip select signal output to the SD-RAM

AA14

DVDD_DDR

-

Power supply terminal (+1.8V)

AA15

DDR_CK

O

Clock signal output to the SD-RAM

AA16

GND

-

Ground terminal

AA17

DDR_DQ[11]

I/O

Two-way data bus with the SD-RAM

AA18

DVDD_DDR

-

Power supply terminal (+1.8V)

AA19,

AA20

DDR_DM[1],

DDR_DM[0]

O

Data mask signal output to the SD-RAM

AA21,

AA22

GND

-

Ground terminal

AA23

DDR_DQ[3]

I/O

Two-way data bus with the SD-RAM

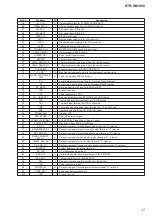

AB1 to

AB3

DDR_DQ[21],

DDR_DQ[19],

DDR_DQ[17]

I/O

Two-way data bus with the SD-RAM

AB4

DDR_DM[2]

O

Data mask signal output to the SD-RAM

AB5

DDR_DQ[30]

I/O

Two-way data bus with the SD-RAM

AB6

DDR_DM[3]

O

Data mask signal output to the SD-RAM

AB7, AB8

DDR_DQ[31],

DDR_DQ[29]

I/O

Two-way data bus with the SD-RAM

AB9 to

AB12

DDR_A[12], DDR_A[6],

DDR_A[3], DDR_A[0]

O

Address signal output to the SD-RAM

AB13

DDR_BA[0]

O

Bank address signal output to the SD-RAM

AB14

DDR_/RAS

O

Row address strobe signal output to the SD-RAM

AB15

DDR_CKE

O

Clock enable signal output to the SD-RAM

AB16

DDR_DQ[12]

I/O

Two-way data bus with the SD-RAM

AB17

DDR_DQS[1]

O

Data strobe signal output to the SD-RAM

AB18 to

AB21

DDR_DQ[8],

DDR_DQ[13],

DDR_DQ[0],

DDR_DQ[5]

I/O

Two-way data bus with the SD-RAM

AB22

DDR_DQS[0]

O

Data strobe signal output to the SD-RAM

AB23

DDR_DQ[4]

I/O

Two-way data bus with the SD-RAM

AC1 to

AC7

DDR_DQ[16],

DDR_DQ[20],

DDR_DQ[22],

DDR_DQ[25],

DDR_DQ[28],

DDR_DQ[27],

DDR_DQ[24]

I/O

Two-way data bus with the SD-RAM

AC8 to

AC12

DDR_A[9], DDR_A[5],

DDR_A[7], DDR_A[1],

DDR_A[10]

O

Address signal output to the SD-RAM

AC13,

AC14

DDR_BA[1],

DDR_BA[2]

O

Bank address signal output to the SD-RAM

AC15

DDR_/WE

O

Write enable signal output to the SD-RAM

AC16

DDR_VREF

O

Reference voltage output to the SD-RAM

AC17

DDR_DQ[10]

I/O

Two-way data bus with the SD-RAM

AC18

DDR_/DQS[1]

O

Data strobe signal output to the SD-RAM

AC19 to

AC21

DDR_DQ[15],

DDR_DQ[7],

DDR_DQ[2]

I/O

Two-way data bus with the SD-RAM

AC22

DDR_/DQS[0]

O

Data strobe signal output to the SD-RAM

AC23

DDR_DQ[1]

I/O

Two-way data bus with the SD-RAM