STR-DN850

75

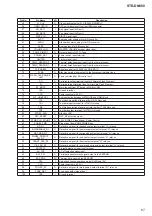

Pin No.

Pin Name

I/O

Description

T1, T2

P[14], P[15]

I

Digital video signal input from the video A/D converter

T3, T4

GND

-

Ground terminal

T7 to T17

GND

-

Ground terminal

T20

HPD_TX2

I

Hot plug detection signal input from the HDMI OUT B connector

T21

GND

-

Ground terminal

T22

TX2_0+

O

TMDS data (positive) output to the HDMI OUT B connector

T23

TX2_0–

O

TMDS data (negative) output to the HDMI OUT B connector

U1, U2

P[10], P[11]

I

Digital video signal input from the video A/D converter

U3, U4

P[12], P[13]

I

Digital video signal input terminal Not used

U7, U8

GND

-

Ground terminal

U9

DVDD

-

Power supply terminal (+1.8V)

U10, U11

GND

-

Ground terminal

U12

DVDD

-

Power supply terminal (+1.8V)

U13, U14

GND

-

Ground terminal

U15

DVDD

-

Power supply terminal (+1.8V)

U16, U17

GND

-

Ground terminal

U20

R_TX2

-

External resistor connection terminal

U21

GND

-

Ground terminal

U22

TX2_C+

O

TMDS clock (positive) signal output to the HDMI OUT B connector

U23

TX2_C–

O

TMDS clock (negative) signal output to the HDMI OUT B connector

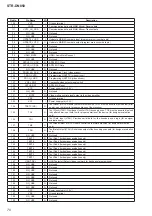

V1 to V4

P[6] to P[9]

I

Digital video signal input from the video A/D converter

V20

GND

-

Ground terminal

V21

PVDD4

-

Power supply terminal (+1.8V)

V22

I

HEAC (positive) signal input terminal Not used

V23

HEAC_2–

I

HEAC (negative) signal input terminal Not used

W1 to W4

P[2] to P[5]

I

Digital video signal input from the video A/D converter

W20

TEST3

-

Test terminal

W21

PVDD6

-

Power supply terminal (+1.8V)

W22

AVDD3

-

Power supply terminal (+1.8V)

W23

NC

-

Not used

Y1, Y2

P[0], P[1]

I

Digital video signal input terminal Not used

Y3

DDR_DQS[2]

O

Data strobe signal output to the SD-RAM

Y4

GND

-

Ground terminal

Y5

DDR_DQ[23]

I/O

Two-way data bus with the SD-RAM

Y6

DVDD_DDR

-

Power supply terminal (+1.8V)

Y7

DDR_DQS[3]

O

Data strobe signal output to the SD-RAM

Y8

GND

-

Ground terminal

Y9

DDR_A[11]

O

Address signal output to the SD-RAM

Y10

DVDD_DDR

-

Power supply terminal (+1.8V)

Y11

DDR_A[4]

O

Address signal output to the SD-RAM

Y12

GND

-

Ground terminal

Y13

DDR_/CAS

O

Column address strobe signal output to the SD-RAM

Y14

DVDD_DDR

-

Power supply terminal (+1.8V)

Y15

DDR_/CK

O

Clock signal output to the SD-RAM

Y16

GND

-

Ground terminal

Y17

DDR_DQ[9]

I/O

Two-way data bus with the SD-RAM

Y18

DVDD_DDR

-

Power supply terminal (+1.8V)

Y19

DDR_DQ[14]

I/O

Two-way data bus with the SD-RAM

Y20

GND

-

Ground terminal

Y21

DDR_DQ[6]

I/O

Two-way data bus with the SD-RAM

Y22

PVDD_DDR

-

Power supply terminal (+1.8V)

Y23

GND

-

Ground terminal

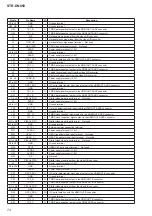

AA1

DDR_DQ[18]

I/O

Two-way data bus with the SD-RAM

AA2, AA3

GND

-

Ground terminal

AA4

DDR_/DQS[2]

O

Data strobe signal output to the SD-RAM

AA5

DDR_DQ[26]

I/O

Two-way data bus with the SD-RAM

Summary of Contents for STR-DN850

Page 104: ...MEMO STR DN850 104 ...