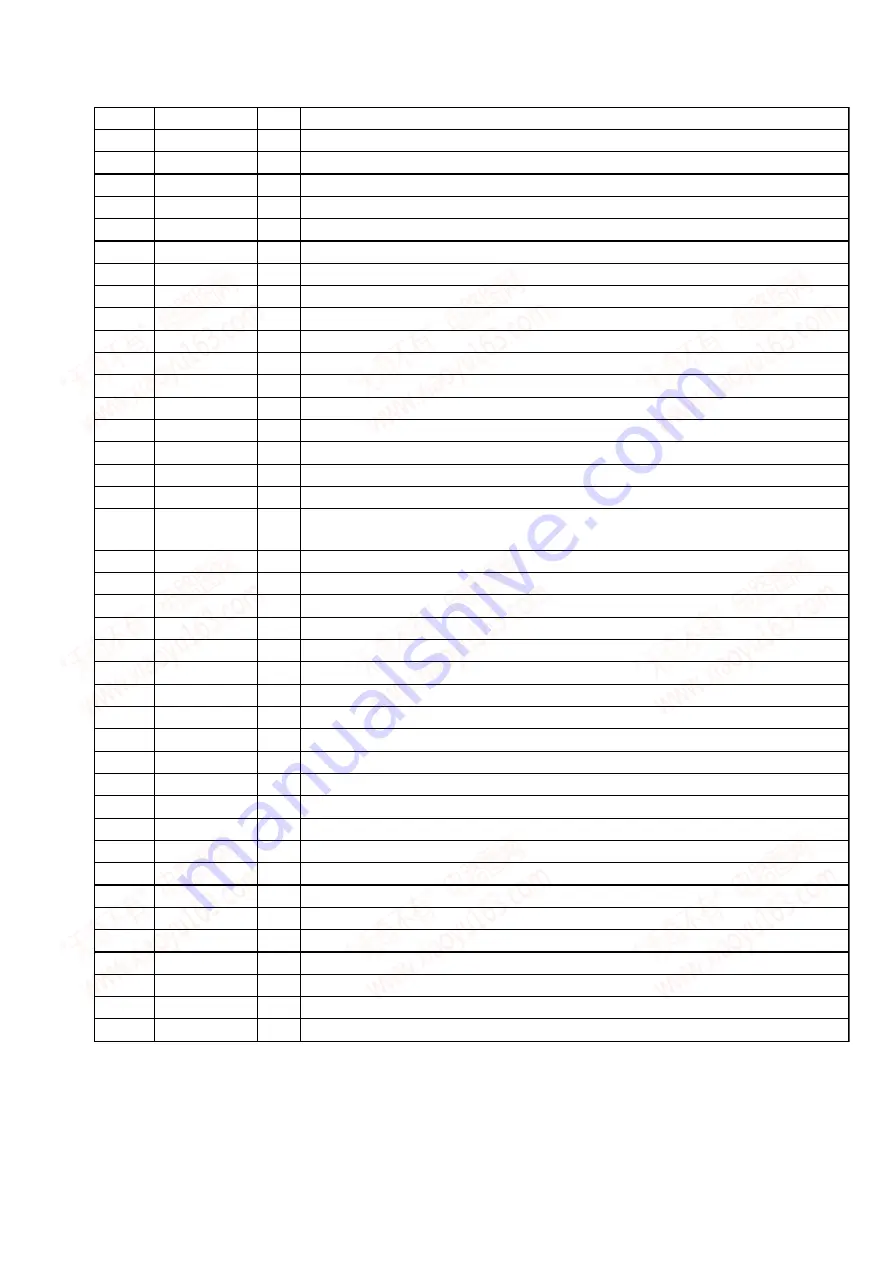

41

STR-KS1000

Pin No.

Pin Name

I/O

Description

57

NO USE

-

Not used

58

LAT2

O

Latch control signal output to the stream processor

59, 60

NO USE

-

Not used

61

SHIFT

O

Shift clock signal output to the stream processor

62

SCDT

O

Serial data output to the stream processor

63

SOFT_MUTE

O

Soft muting on/off control signal output to the stream processor "L": muting on

64

INT

O

Reset signal output to the stream processor "L": reset

65

LAT1

O

Latch control signal output to the stream processor

66

TUNED

I

Tuning detection signal input from the tuner "L": tuned

67

TUNER LED

O

LED drive signal output of the tuner indicator "L": LED on

68

OVF

I

Over flow status input from the stream processor (front/surround/center)

69

LAT3

O

Latch control signal output to the stream processor

70, 71

VOLB, VOLA

I

Jog dial pulse input from the rotary encoder (for MASTER VOLUME)

72

FL_DIN

O

Serial data output to the fluorescent indicator tube

73

FL_CLK

O

Serial data transfer clock signal output to the fluorescent indicator tube

74

FL_STB

O

Strobe signal output to the fluorescent indicator tube

75, 76

NO USE

-

Not used

77

RSTX

I

System reset signal input terminal "L": reset

For several hundreds msec. after the power supply rises, "L" is input, then it change to "H"

78

OVFW

I

Over flow status input from the stream processor (sub woofer)

79, 80

X1A, X0A

-

Not used

81

VSS

-

Ground terminal

82

X0

I

System clock input terminal (24 MHz)

83

X1

O

System clock output terminal (24 MHz)

84

VCC3

-

Power supply terminal (+3.3V)

85

T.CLK

O

PLL serial data transfer clock signal output to the tuner

86

T.DATA

O

PLL serial data output to the tuner

87

SLATCH

O

Latch control signal output to the tuner

88

T_DO

I

PLL serial data input from the tuner

89

T_MUTE

O

Tuner muting on/off control signal output to the tuner

90

ST

I

FM stereo detection signal input from the tuner

-

Not used

O

Signal switch signal output terminal Not used

O

System reset signal output to the digital audio interface receiver "L": reset

O

Output clock selection signal output to the digital audio interface receiver

O

Serial data transfer clock signal output to the digital audio interface receiver

O

Chip enable signal output to the digital audio interface receiver

O

Serial data output to the digital audio interface receiver

I

Serial data input from the digital audio interface receiver

I

PLL lock error signal and data error flag input from the digital audio interface receiver

100

XSTATE

I

Source clock selection monitor input from the digital audio interface receiver

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299