STR-DG820

STR-DG820

31

31

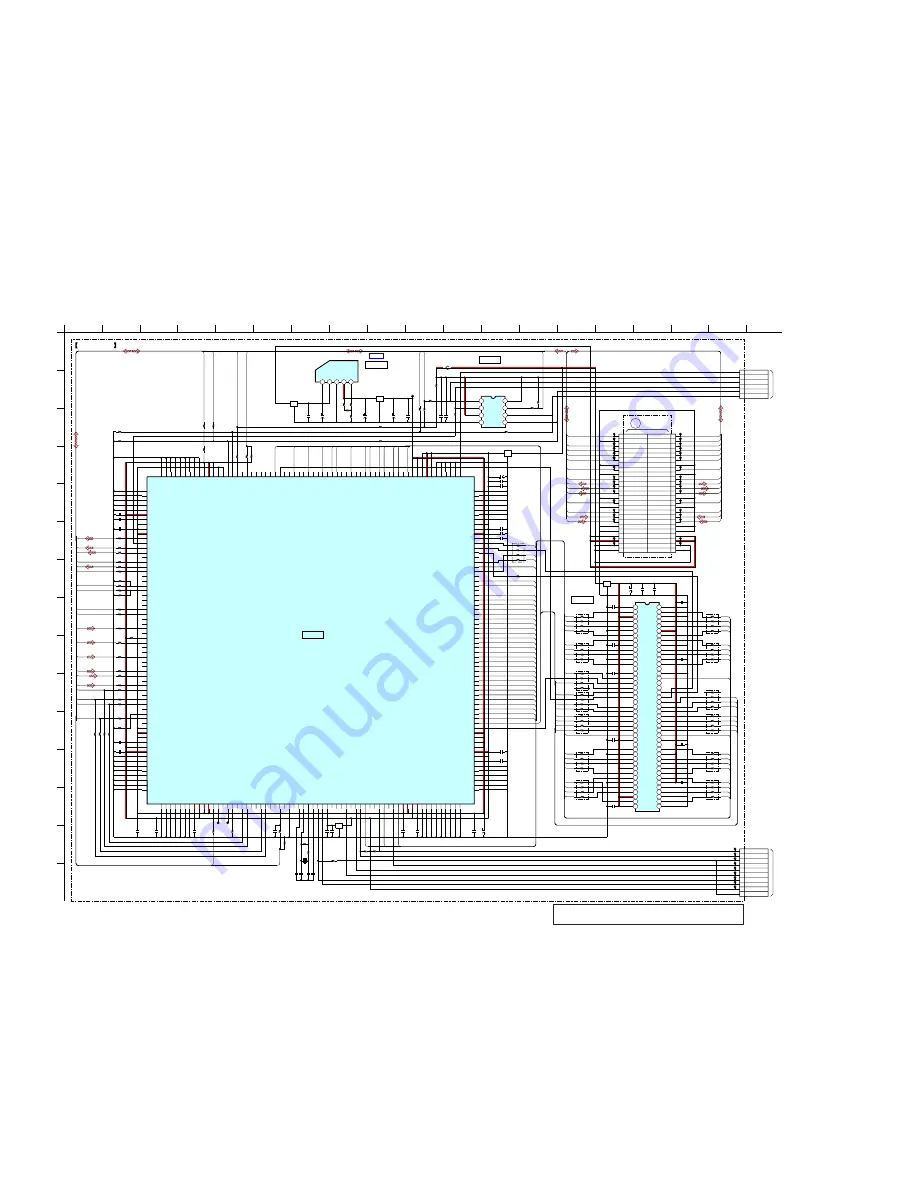

• See page 48 for IC Block Diagrams. • See page 56 for IC Pin Function Description.

6-17. SCHEMATIC DIAGRAM - DSP Board -

Note:

When IC5021 cannot exchange with single. When IC5021

is damaged, exchange the entire mounted board.

X

BOARD

(1/2)

CN2206

DIGITAL AUDIO

IC B/D

10

C5095

10

C5091

10k

R5002

0.1

C5088

0.1

C5012

0.1

C5094

CL5005

CL5004

CL5001

CL5002

CL5003

CL5036

FB5003

1

2

3

4

5

SI-3011ZD-TL

IC5015

VC

VIN

GND

VOUT

SENSE

CL5044

CL5045

CL5046

CL5047

CL5048

CL5051

CL5052

0.1

C5117

0.1

C5120

0.1

C5126

0.1

C5132

0.1

C5139

0.1

C5140

0.1

C5144

0.1

C5150

0.1

C5155

6.3V

470

C5161

6.3V

470

C5162

1M

R5280

8p

C5163

8p

C5164

470p

C5165

470p

C5166

8

7

6

5

4

3

2

1

SST25VF016B-50-4C-S2AF-T

IC5020

CE#

SO

WP#

VSS

CL5059

0.1

C5168

22

R5321

22

R5322

22

R5323

22

R5324

22

R5325

22

R5326

22

R5327

22

R5331

22

R5332

22

R5333

22

R5334

22

R5335

22

R5336

22

R5337

22

R5341

22

R5346

22

R5347

22

R5348

22

R5349

1k

R5350

CL5062

10

C5170

10k

R5355

CL5102

CL5104

CL5105

CL5107

CL5108

CL5109

CL5110

CL5111

CL5112

CL5113

CL5114

CL5115

CL5116

CL5117

CL5118

CL5120

CL5121

CL5139

1k

R5357

1k

R5358

1k

R5359

6.3V

220

C5172

10P

CN5003

0.1

C5173

0.1

C5175

0.1

C5176

0.1

C5177

0.1

C5178

0.1

C5179

0.1

C5180

0.1

C5181

0.1

C5182

10

C5183

10k

R5363

10k

R5368

10k

R5369

22

R5375

22

R5376

22

R5377

1k

R5379

CL5152

CL5153

CL5156

CL5157

CL5158

CL5159

CL5160

CL5161

CL5162

CL5163

CL5164

EMI

FL5006

EMI

FL5009

EMI

FL5010

EMI

FL5011

10

C5185

EMI

FL5013

220

RB021

220

RB022

220

RB024

220

RB019

220

RB026

220

RB025

100

RB009

100

RB010

P1

100

RB012

100

RB013

P1

100

RB014

100

RB015

100

RB016

47

R5290

470

R5365

10k

R5373

22

R5384

22

R5385

50P

CN5001

SFLASH_HOLD#

SFLASH_CE#

SPIO_ENA#

SPIO_MISO

DSP_INT

NON_AU

GND

MCK

GND

SI_G

SI_E

SI_C

SI_A

GND

BCK_OUT

GND

SO_E

SO_C

SO_A

GND

GND

VDDINT

VDDINT

VDDEXT

GND

BCK

GND

LRCK

SI_F

SI_D

SI_B

GND

LRCK_OUT

GND

SO_F

SO_D

SO_B

GND

GND

VDDINT

VDDINT

VDDEXT

SPIO_CLK

GND

SPIO_CS#

SPIO_MOSI

DSP_RESET

ERROR

VDDEXT

VDDEXT

CL5165

22

R5386

22

R5387

10k

R5391

10k

R5392

0

R5393

22

R5394

R5397

10k

R5399

10k

R5402

10k

22

R5403

22

R5404

22

R5405

22

R5406

22

R5407

6.3V

470

C5188

10

C5189

M12L64322A-6TG

IC5022

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

NC

VDD

DQM0

WE#

CAS#

RAS#

CS#

NC

BA0

BA1

A10/AP

A0

A1

A2

DQM2

VDD

NC

DQ16

VSSQ

DQ17

DQ18

VDDQ

DQ19

DQ20

VSSQ

DQ21

DQ22

VDDQ

DQ23

VDD

0.1

C5195

0.1

C5196

0.1

C5197

0.1

C5198

0.1

C5199

0.1

C5200

0.1

C5201

0.1

C5202

10k

R5410

R5299 10k

CL5166

6.3V

220

C5001

22

R5411

22

R5412

22

R5413

22

R5414

180

R5279

1k

R5378

H1

1

J1

1

J10

K16

K1

1

L12

M13

J14

R16

K12

J12

P16

P15

N16

N15

N14

M16

M15

M14

L16

L15

L14

L13

K15

K14

K13

J16

J15

J13

H15

H13

H14

H16

G13

G14

G15

F13

F14

F15

F16

E14

E15

E16

D14

D15

D16

C14

C15

C16

B15

G12

H12

E13

D13

B16

G16

A16

E12

F12

F1

1

G1

1

G10

H10

H9

VSS

G9

VSS

A10

VSS

F10

VSS

F9

VSS

F8

DVDD

D12

DVDD

A15

CVDD

E11

CVDD

E10

CVDD

E9

AXR0[0]

A14

SPI0_SOMI

B14

AXR0[2]

A13

AXR0[1]

B13

ACLKR2

C13

AXR0[4]

A12

AXR0[3]

B12

AFSR2

C12

AXR0[6]/SPI1_ENA#

A11

AXR0[5]/SPI1_SCS#

B11

AFSX2

C11

ACLKX2

D11

AXR0[7]/SPI1_CLK

B10

UHPI_HCNTL[1]

C10

AMUTE2_HINT#

D10

AXR0[9]/AXR1[4]/SPI1-SIMO

A9

AXR0[8]/AXR1[5]/SPI1_SOMI

B9

UHPI_HAS#

C9

UHPI_HCNTL[0]

D9

AXR0[10]/AXR1[3]

B8

UHPI_HRW

D8

UHPI_HCS#

C8

AXR0[11]/AXR1[2]

A8

UHPI_HDS[1]#

D7

UHPI_HDS[2]#

C7

AXR0[12]/AXR1[1]

B7

UHPI_HRDY#

D6

UHPI_HBE[0]#

C6

AXR0[13]/AXR1[0]

B6

AXR0[14]/AXR2[1]

A6

UHPI_HBE[1]#

C5

AXRO[15]/AXR2[0]

B5

ACLKR0

A5

UHPI_HBE[2]#

C4

AFSR0

B4

ACLKXO

A4

UHPI_HD[23]

C3

AHCLKR0/AHCLKR1

B3

AFSX0

A3

UHPI_HBE[3]#

B2

CVDD

E6

CVDD

E7

CVDD

E8

DVDD

A2

DVDD

D4

DVDD

D5

VSS

H8

VSS

G7

VSS

G8

VSS

F6

VSS

F7

VSS

E5

VSS

A1

VSS

A7

K4

K3

K2

L4

L3

L2

J9

K9

K8

L8

L7

T7

N5

P8

T2

M6

M7

M8

M9

T3

R3

T4

R4

P4

T5

R5

P5

T6

R6

P6

N6

R7

P7

N7

T8

R8

N8

T9

P9

N9

R9

N10

P10

R10

N11

P11

R11

T11

P12

R12

T12

N13

P13

R13

T13

P14

R14

T14

R15

M11

M10

N12

T15

T16

T10

M12

L11

L10

L9

K10

6P

CN5002

16V

47

C5007

25MHz

X002

D7

D6

D5

D4

D3

D0

D1

D2

D21

D15

D14

D13

D12

A2

A1

A0

A10

A3

A4

A5

A6

A7

A8

A9

DQM1

BA0

DQM2

DQM3

BA1

A0

A1

A2

A10

A3

A4

A5

A6

A7

A8

A9

BA1

BA0

RAS#

CAS#

D11

D10

D9

D8

DQM0

D0

D1

D7

D5

D6

D3

D4

D2

D14

D15

D13

D12

D11

D10

D9

D8

D31

D30

D27

D26

D25

D24

D21

D20

D19

D18

D17

D16

D22

SO_B

SO_A

SO_D

SI_A

SI_C

SI_D

SI_E

SI_F

D29

D23

D28

D28

D29

D31

D30

CAS#

D24

D27

D26

D25

D23

RAS#

SO_C

D20

D22

DQM1

DQM2

DQM3

D19

D18

D17

D16

SO_F

SI_B

SI_G

SO_B

LRCK

BCK

SPI0_SCK

DSP_LRCK

SO_D

SO_F

SI_B

SI_D

SI_F

DSP_RESET#

SPI0_SIMO

SPI0_CS#

MCK

LRCK

DSP_LRCK

BCK

DSP_BCK

SO_E

NON_AUDIO

ERR

DSP_INT

DSP_RESET#

DQM0

ERR

SFLASH_HOLD#

SFLASH_CE#

SPI0_SCK

IC5020

SERIAL FLASH

DSP BOARD

(NC)

(NC)

7

11

D

B

16

6

9

17

10

F

5

N

15

L

K

19

3

G

1

18

12

C

M

E

H

8

J

4

13

A

14

2

I

O

SI

SCK

HOLD#

VDD

VSS

VSS

VSS

VSS

VSS

VSS

DVDD

DVDD

DVDD

CVDD

CVDD

EM_A[9]

EM_A[1

1]

EM_A[7]

EM_A[8]

UHPI_HD[6]

EM_A[5]

EM_A[6]

UHPI_HD[2]

EM_A[3]

EM_A[4]

UHPI_HD[4]

UHPI_HD[3]

EM_A[2]

UHPI_D[1]

UHPI_HD[0]

EM_A[0]

EM_A[1]

UHPI_HD[15]

EM_A[10]

UHPI_HD[14]

UHPI_HD[13]

EM_BA[1]

UHPI_HD[12]

UHPI_HD[1

1]

EM_BA[0]

UHPI_HD[10]

UHPI_HD[9]

EM_CS[0]#

EM_RAS#

UHPI_HD[8]

EM_CS[2]#

EM_R

W

EM_W

AIT

EM_OE#

SPI0_ENA#

AHCLKR2

SPI0_SCS#

SPI0_CLK

SPI0_SIMO

CVDD

CVDD

DVDD

DVDD

DVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

DVDD

DVDD

DVDD

CVDD

CVDD

CVDD

CVDD

EM_WE#

EM_CAS#

EM_D[7]

EM_DQM[0]

EM_D[20]

EM_D[5]

EM_D6]

EM_D[19]

EM_D[3]

EM_D[4]

EM_D[17]

EM_D[18]

EM_D[2]

EM_D[31]

EM_D[16]

EM_D[0]

EM_D[1]

EM_D[30]

EM_D[14]

EM_D[28]

EM_D[29]

EM_D[15]

EM_D[27]

EM_D[26]

EM_D[13]

EM_D[25]

EM_D[24]

EM_D[12]

EM_D[11]

EM_A[12]

EM_D[10]

EM_D[9]

UHPI_HD[5]

EM_DQM[2]

EM_D[8]

EM_DQM[1]

UHPI_HD[7]

EM_CLK

EM_CKE

EM_DQM[3]

CVDD

CVDD

DVDD

DVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

DVDD

DVDD

CVDD

CVDD

AHCLKX0/AHCLKX2

AMUTE0

UHPI_HD[22]

AMUTE1

AHCLKX1

UHPI_HD[21]

ACLKX1

ACLKR1

UHPI_HD[20]

UHPI_HD[19]

AFSX1

AFSR1

UHPI_HD[18]

UHPI_HD[17]

RESET#

UHPI_HD[31]

CLKIN

UHPI_HD[16]

OSCVDD

OSCIN

OSCOUT

OSCVSS

TRST#

TMS

PLLHV

UHPI_HD[29]

UHPI_HD[28]

UHPI_HD[30]

TDI

UHPI_HD[27]

TDO

EMU[0]#

EM_D[22]

UHPI_HD[26]

UHPI_HD[25]

EMU1#

EM_D[21]

UHPI_HD[24]

TCK

EM_D[23]

CVDD

CVDD

DVDD

DVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D790E002BZDH300

IC5021

(Chip Size Package)

CSP

IC5021

DSP

+1.26V REGULATOR

IC5015

SPI0_ENA#

SPI0_SIMO

SPI0_SOMI

SPI0_CS#

L1

M3

M2

M1

N4

N3

N2

N1

P3

P2

P1

R2

J5

K5

M4

R1

T1

K1

M5

L5

L6

K6

K7

J7

J8

H7

J6

H6

G6

F5

H3

G1

B1

E4

H5

G5

C2

C1

D3

D2

D1

E3

E2

E1

F4

F3

F2

F1

G4

G3

G2

H4

H2

H1

J4

J2

J3

J1

9

1

2

3

4

5

6

7

8

10

11

12

13

14

15

16

17

18

19

20

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

39

38

37

36

35

21

22

34

33

23

24

32

25

31

30

29

26

27

28

48

53

56

49

50

51

55

54

52

47

46

45

44

57

58

59

60

61

62

63

43

42

41

40

VSS

DQ24

VSSQ

DQ25

DQ26

VDDQ

DQ27

DQ28

VSSQ

DQ29

DQ30

VDDQ

DQ31

NC

VSS

DQM3

A3

A4

A5

A6

A7

A8

A9

CKE

CLk

NC

NC

DQM1

VSS

NC

DQ8

VDDQ

DQ9

DQ10

VSSQ

DQ11

DQ12

VDDQ

DQ13

DQ14

VSSQ

DQ15

VSS

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

1

2

3

4

5

6

7

8

9

10

EMU1

EMU0

GND

TCK

TDO

TDI

TRST#

TMS

+3.3V

GND

SO_A

SO_C

SO_E

DSP_BCK

SI_A

SI_C

SI_E

SI_G

MCK

NON_AUDIO

DSP_INT

SPI0_SOMI

SPI0_ENA#

SFLASH_CE#

SFLASH_HOLD#

GND

+3.3V

XRESET

SO

SI

SCK

1

2

3

4

5

6

100

RB011

IC5022

SD-RAM

(Page

34)

Summary of Contents for STRDG820 - STR AV Receiver

Page 95: ...MEMO STR DG820 95 ...