TA-DA9000ES

24

24

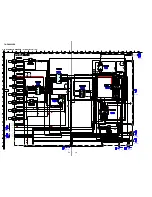

6-2.

BLOCK DIAGRAM – A/D CONVERTER Section –

6

7

2

3

1

AMP

IC115

A/D CONVERTER

IC2011

A/D CONVERTER

IC2031

A/D CONVERTER

IC2021

A/D CONVERTER

IC2041

4 VINL+

5 VINL–

6

7

2

3

1

AMP

IC114

17 VINR+

16 VINR–

11

DSDL

9

SCKI

10

BCK

12

DSDR

AD-L

AD-R

6

7

2

3

1

AMP

IC119

4 VINL+

5 VINL–

6

7

2

3

1

AMP

IC118

17 VINR+

16 VINR–

11

DSDL

10

BCK

12

DSDR

AD-C

AD-W

6

7

2

3

1

SR-CH

R-CH

SBR-CH

AMP

IC117

4 VINL+

5 VINL–

6

7

2

3

1

AMP

IC116

17 VINR+

16 VINR–

11

DSDL

10

BCK

DSDR

AD-SL

AD-SR

6

7

2

3

1

AMP

IC121

4 VINL+

5 VINL–

6

7

2

3

1

AMP

IC120

17 VINR+

16 VINR–

11

DSDL

10

BCK

DSDR

AD-SBL

1/2 DIVIDER

IC2051

(Page 28)

6

• SIGNAL PATH

• R-CH is omitted due to same as L-CH.

: AUDIO (DIGITAL)

: AUDIO (ANALOG)

L

C

W

SL

SBL

VREF

VREF

+15V

VREF

VREF

VREF

VREF

VREF

VREF

VREF

+5V REGULATOR

IC113

9

DSDL

9

DSDL

9

DSDL

12

(Page 23)

4

AD-BCK

AD-SBR

22.5792

595C

I LINK/AD512

I LINK/AD512

B+ SWITCH

Q2302, 2303

D3.3V

I512

HATS ON/OFF

(Page 27)

7

(Page 28)

8

(Page 25)

10

(Page 26)

9

12

OSC

IC2304

X2301

22.5792MHz

CLOCK SELECT

IC2306

SWITCHING

IC2308

D2301