4-2

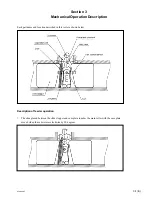

UYA-S90SF

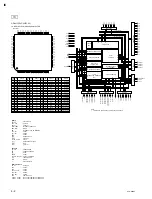

IC

[|IC|]

HD6413004F (HITACHI)

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

16-BIT SINGLE CHIP MICROCOMPUTER

—TOP VIEW—

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

PB0/TIOCA3

PB1/TIOCB3

PB2/TIOCA4

PB3/TIOCB4

PB4/TOCXA4

PB5/TOCXB4

PB6

PB7/

ADTRG

P90/T

X

D

P92/R

X

D

P94/SCK/

IRQ4

GND

D0

D1

D2

D3

D4

D5

D6

D7

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

—

O

O

O

O

O

O

O

O

—

O

O

O

O

O

O

O

O

O

O

V

CC

A0

A1

A2

A3

A4

A5

A6

A7

GND

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

O

O

I/O

I

I

O

I

I

I

—

I

I

—

O

O

O

O

—

I

I

A18

A19

P60/

WAIT

MD0

MD1

Ø

STBY

RES

NMI

GND

EXTAL

XTAL

V

CC

AS

RD

WR

RESO

A.GND

P70/AN0

P71/AN1

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

I

I

I

I

I

I

I

—

I/O

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

P72/AN2

P73/AN3

P74/AN4

P75/AN5

P76/AN6

P77/AN7

V

REF

A.V

CC

P80/

IRQ0

P81/

IRQ1

P82/

IRQ2

P83/

IRQ3

PA0/TCLKA

PA1/TCLKB

PA2/TIOCA0/TCLKC

PA3/TIOCB0/TCLKD

PA4/TIOCA1/A23

PA5/TIOCB1/A22

PA6/TIOCA2/A21

PA7/TIOCB2/A20

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

INPUTS

ADTRG

AN0 - AN7

EXTAL

IRQ0

-

IRQ4

MD0, MD1

NMI

P70 - P77

P81 - P83

RES

R

X

D

STBY

TCLKA - TCLKD

V

REF

WAIT

XTAL

OUTPUTS

A0 - A19

AS

RD

RESO

TOCXA4, TOCXB4

T

X

D

WR

Ø

INPUTS/OUTPUTS

D0 - D7

P60

P80

P90, P92, P94

PA0 - PA7

PB0 - PB7

SCK

TIOCA0 - TIOCA4

TIOCB0 - TIOCB4

: A/D TRIGGER

: ANALOG

: CRYSTAL

: INTERRUPT REQUEST

: MODE

: INTERRUPT FOR NO MASKING

: PORT7

: PORT8

: RESET

: RECEIVE DATA

: STANDBY

: CLOCK

: REFERENCE VOLTAGE

: WAIT

: CRYSTAL

: ADDRESS BUS

: ADDRESS STROBE

: READ

: RESET

: OUTPUT COMPARE

: TRANSMIT DATA

: WRITE

: SYSTEM CLOCK

: DATA BUS

: PORT6

: PORT8

: PORT9

: PORT A

: PORT B

: SERIAL CLOCK

: INPUT CAPTURE/OUTPUT COMPARE

: INPUT CAPTURE/OUTPUT COMPARE

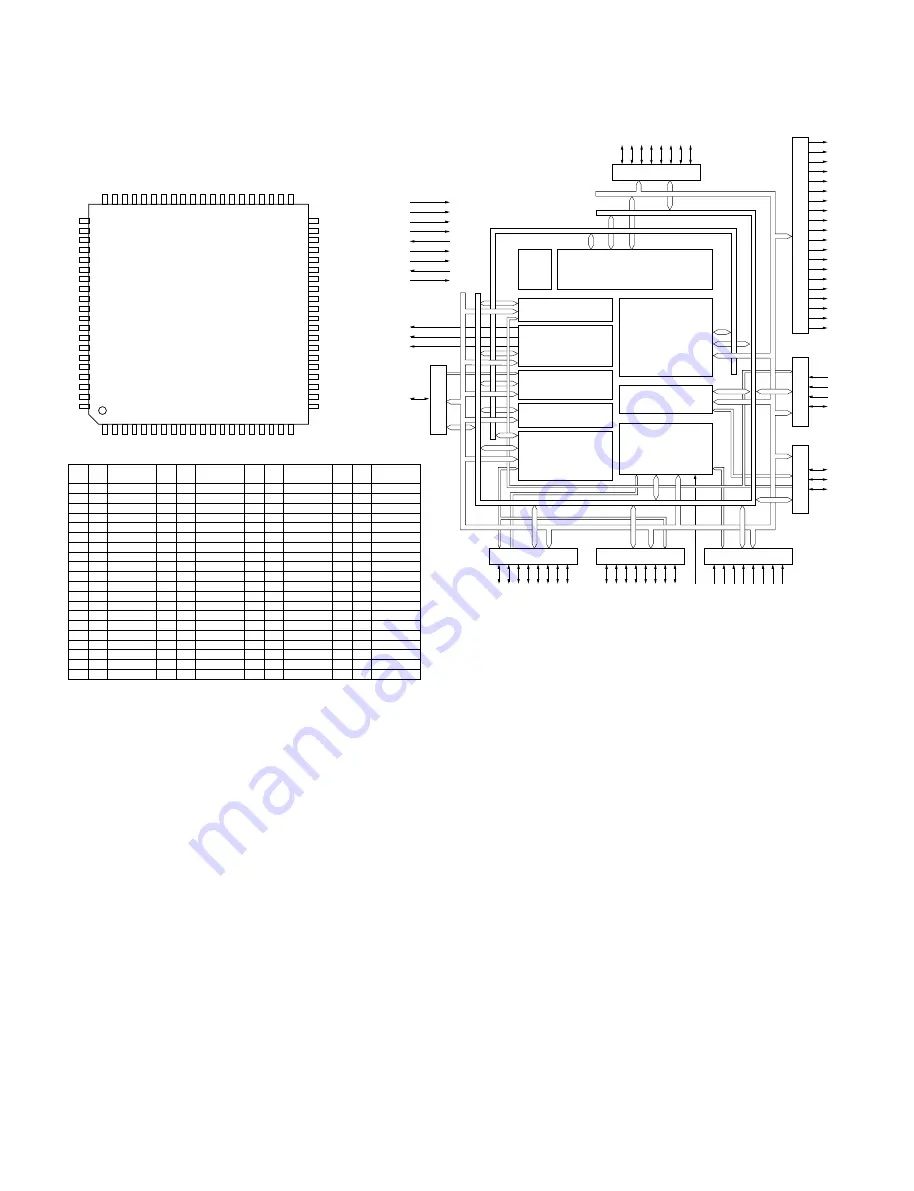

WR

56

RD

55

AS

54

P60/

WAIT

43

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

42

41

40

39

38

37

36

35

34

33

32

31

29

28

27

26

25

24

23

22

NMI

49

RESO

57

PB7/

ADTRG

PB6

PB5/TOCXB4

PB4/TOCXA4

PB3/TIOCB4

PB2/TIOCA4

PB1/TIOCB3

PB0/TIOCA3

8

7

6

5

4

3

2

1

PA7/TIOCB2/A20

PA6/TIOCA2/A21

PA5/TIOCB1/A22

PA4/TIOCA1/A23

PA3/TIOCB0/TCLKD

PA2/TIPCA0/TCLKC

PA1/TCLKB

PA0/TCLKA

80

79

78

77

76

75

74

73

P77/AN7

P76/AN6

P75/AN5

P74/AN4

P73/AN3

P72/AN2

P71/AN1

P70/AN0

66

65

64

63

62

61

60

59

V

REF

67

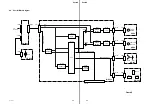

ADDRESS BUS

DATA BUS

PORT 8

PORT 6

PORT 9

PORT 7

PORT A

PORT B

P83/

IRQ3

P82/

IRQ2

P81/

IRQ1

P80/

IRQ0

72

71

70

69

P94/SCK/

IRQ4

P92/R

X

D

P90/T

X

D

11

10

9

D7

D6

D5

D4

D3

D2

D1

D0

20

19

18

17

16

15

14

13

RES

48

STBY

47

Ø

46

XTAL

52

EXTAL

51

MD0

44

MD1

45

CLOCK

OSC.

H8/300H CPU

INTERRUPT CONTROLLER

BUS CONTROLLER

WATCHDOG TIMER

16 BIT

INTEGRATED TIMER UNIT

(ITU)

WAIT-STATE

CONTROLLER

SERIAL COMMUNICATION

INTERFACE (SCI)

x

1 CHANNEL

RAM

*

2K BYTES

A/D CONVERTER

ADDRESS BUS

DATA BUS (UPPER)

DATA BUS (LOWER)

NOTE

*

: 2K BYTES IN THE H8/3004, 4K BYTES IN THE H8/3005.