18

18

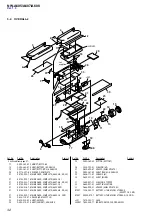

NW-A605/A607/A608

NW-A605/A607/A608

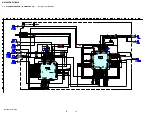

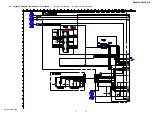

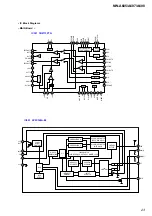

4-6. SCHEMATIC DIAGRAM – MAIN BOARD (3/6) –

VDR405

VDR402

R453

R423

C

4

0

5

C

4

04

R432

R433

R430

R431

R713

R424

R419

C701 C703

C

7

0

5

C

4

2

0

C

4

2

3

C

4

0

1

C417

C400

R722

TP405

TP404

C406

T

P

4

0

6

TP418

TP409

TP411

R420

R

3

7

2

9

R

7

3

2

R

7

3

3

R

7

3

5

TP417

TP416

R421

TP408

TP415

C419

C421

C415

C

41

6

R

4

1

2

R

4

1

8

R

4

04

C

4

1

8

C

4

2

2

C414

X400

R

4

1

0

R

4

11

C409

C

4

1

0

C411

C

4

0

8

R409

TP420

TP419

R467

R402

R

4

0

8

R

4

1

7

R

4

0

7

R

4

0

6

R

4

0

5

C

4

0

7

R

2

4

0

3

R

2

4

1

7

R

4

1

4

R401

C

4

0

2

C

4

0

3

R416

TP412

R711

R715

R716

R717

TP701

TP700

470k

470k

0

.1

0

.1

220

10

220

220

470

10k

10k

0.01 0.01

0

.0

1

1

0

0

0p

1

0

0

0

p

0

.1

0.1

0.1

470k

RXD1

TXD1

0.1

R

S

T

XMS

XBOOT

MSID0

10k

0

0

0

0

MSBS

MSSCLK

100k

MSINS

MSPWR

0.1

0.1

10p

1

0

p

2

20

2

20

2

2

0

0

.1

0

.1

0.1

22.579MHz

1

0

0

1

M

0.1

4.7

1

1

22

USB1DP

USB1DM

2.2M

2.2M

2.2

k

4

.7

k

2

2

2

2

0

0.1

2

2

0

2

2

0

1

0

k

0

4

.7

4

.7

10k

DEBUG

10k

10k

10k

10k

ADK2

ADK

• See page 12 for Waveform. • See page 26 for IC Pin Function Description.