4-4

WRR-802A (U)

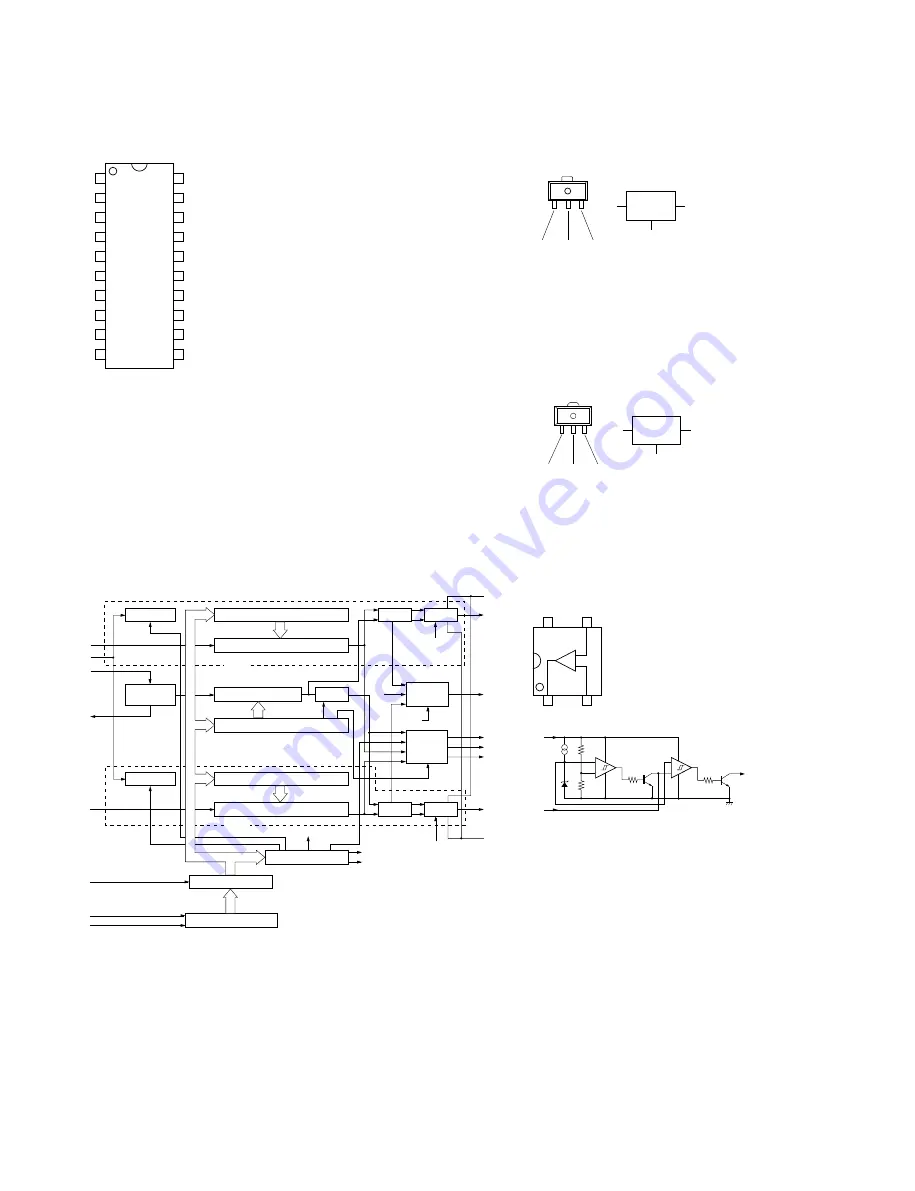

IC

MB15U10PFV-ER (FUJITSU)

OUT

1

GND

2

IN

3

3

1

2

IN

OUT

GND

POSITIVE VOLTAGE REGULATOR

—SIDE VIEW—

COMMON

1

IN

2

OUT

3

2

3

1

COMMON

IN

OUT

NEGATIVE VOLTAGE REGULATOR

—SIDE VIEW—

NJM78L12UA-TE1 (JRC)

+

12 V(0.1 A)

TA78L05F-TE12L (TOSHIBA)

NJM79L12UA (JRC)

_

12 V (100 mA)

NJM79L12UA(TE1)

PST575EMT-T1 (MITSUMI)

GND

V

CC

SYSTEM RESETTING

—TOP VIEW—

4

1

2

3

+

_

C

IN

OUT

+

_

+

_

1

V

CC

3

C

IN

2

OUT

P1/fp1

P2/fp2

Do1

V

CC

1

PS

fin1

D.GND

OSCin

P3/fr2

OSCout

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

I

SET

P0/LD

Vp

Do2

A.GND

fin2

V

CC

2

LE

Data

Clock

PLL FREQUENCY SYNTHESIZER WITH PRE-SCALER

—TOP VIEW—

INPUTS

Clock

Data

fin1, fin2

I

SET

LE

OSCin

PS

Vp

OUTPUTS

Do1, Do2

OSCout

P0 - P3

LD

fp1, fp2

fr2

: CLOCK

: DATA

: RF (PLL1, 2)

: CHARGE PUMP OUTPUT CURRENT ADJUSTMENT

: LOAD ENABLE OF SERIAL INPUT DATA (H : DATA IS SHIFTED INTO A LATCH)

: CRYSTAL OSCILLATOR OR TCXO

: POWER SAVING MODE CONTROL (L : POWER SAVING MODE)

: POWER SUPPLY FOR CHARGE PUMP

: CHARGE PUMP (PLL1, 2)

: CRYSTAL OSCILLATOR

: DATA

: LOCK DETECTOR

: fp1, fp2 MONITORING

: fr2 MONITORING

POWER SAV-

POWER SAV-

CRYSTAL

OSCILLATOR

PHASE

CHARGE

17-BIT LATCH (COMPARISONAL DIVISION)

MAIN COUNTER

PLL1

14-BIT LATCH (REFERENCIAL DIVISION)

17-BIT LATCH (COMPARISONAL DIVISION)

MAIN COUNTER

10-BIT LATCH

LATCH SELECTOR

REFERENCE COUNTER

+

1/

+

2

CHARGE

PHASE

SHIFT REGISTER (21-BIT)

SELECTOR

SELECTOR

6

fin1

8

OSCin

5

PS

10

OSCout

15

fin2

13

LE

12

Data

11

Clock

PS1

fp1

LD1

CR1

ISET

P0

LD2

fp2

fp2

P1, 2, 3

P0

fp1

fr2

OLA, B

CR2

PS2

SR

TS

fr2

fr1

OLA, B

CR1, 2

18

Vp

3

Do1

19

P3/fr2

P0/LD

9

P1/fp1

1

P2/fp2

2

Do2

17

I

SET

20

PLL2