– 17 –

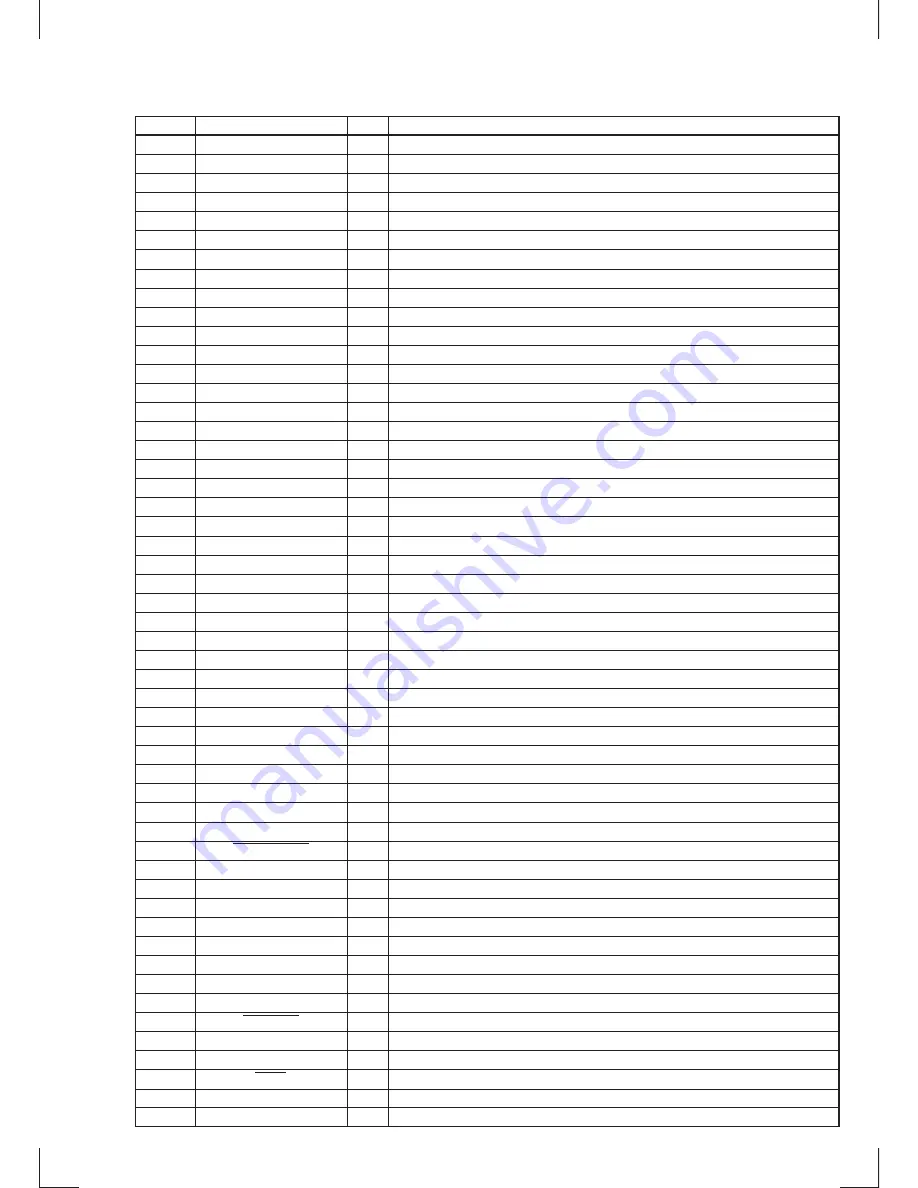

• IC401 HD6432655H01FN (SYSTEM CONTROL)

Pin No.

Pin Name

I/O

Pin Description

1

DAB LOCKIN

I

Lock input for PLL.

2

PG4

—

Connect to ground.

3

VSS

—

Ground

4

NIL

—

Ground

5

VCC

—

Power supply pin (+5 V)

6 – 9

A0 – 3

O

Address data signal output

10

VSS

—

Ground

11 – 18

A4 – 11

O

Address data signal output

19

VSS

—

Ground

20 – 26

A12 – 18

O

Address data signal output

27

PA3

I

Test pin (Connect to ground.)

28

VSS

—

Ground

29

PA4

I

Test pin (Connect to ground.)

30

PA5

I

Connect to ground.

31

PA6

I

Reserve IRQ PULL UP signal input

32

MPEGHREQ

I

Reserve IRQ PULL UP signal input

33

MPEGREQ

I

MPEG interruption signal input

34

MREQ

I

Interruption input from PRIMO synchronization.

35, 36

VSS

—

Ground

37

XVFICID

I

PRIMO frame interruption signal input (24 ms)

38

BUSON

I

Interruption input from serial bus.

39

VCC

—

Power supply pin (+5 V)

40 – 43

D0 – 3

I/O

Data bus signal input/output

44

VSS

—

Ground

45 – 52

D4 – 11

I/O

Data bus signal input/output

53

VSS

—

Ground

54 – 57

D12 – 15

I/O

Data bus signal input/output

58

VCC

—

Power supply pin (+5 V)

59

MBUSSO

O

M bus data signal output

60

UNISO

O

Serial bus data signal output

61

MBUSSI

I

M bus data signal input

62

UNISI

I

Serial bus data signal input

63

MBUSCKO

O

M bus clock signal output

64

UNICKI

I

Serial bus clock signal input

65

VSS

—

Ground

66

FSCONV ERRIN

I

FSCONV error signal input

67, 68

VSS

—

Ground

69

DRC BUSYIN

I

DRC status read signal input

70

XMPEG RST

O

MPEG reset signal output (Reserve)

71

SEL G

O

Data select signal output. L : Data change

72

S OUT

O

Serial bus data signal output

73

S CKO

O

Serial bus clock signal output

74 – 76

SEL 2 – 0

O

Data select signal output

77

DAC MUT

O

DAC mute signal output. H : Mute on

78

XA MUT

O

Analog mute signal output. L : Mute on

79

XDRC MUT

O

DRC mute signal output. L : Mute on

80

WDTOVF

—

Watch dog (Open)

81

SYSRST

I

System reset signal input

82

BU IN

I

Battry power supply check signal input

83

STBY

I

Standby signal input

84

VCC

—

Power supply pin (+5 V)

85

XTAL

I

System clock signal input (18.432 kHz)