25

XVM-H65

49

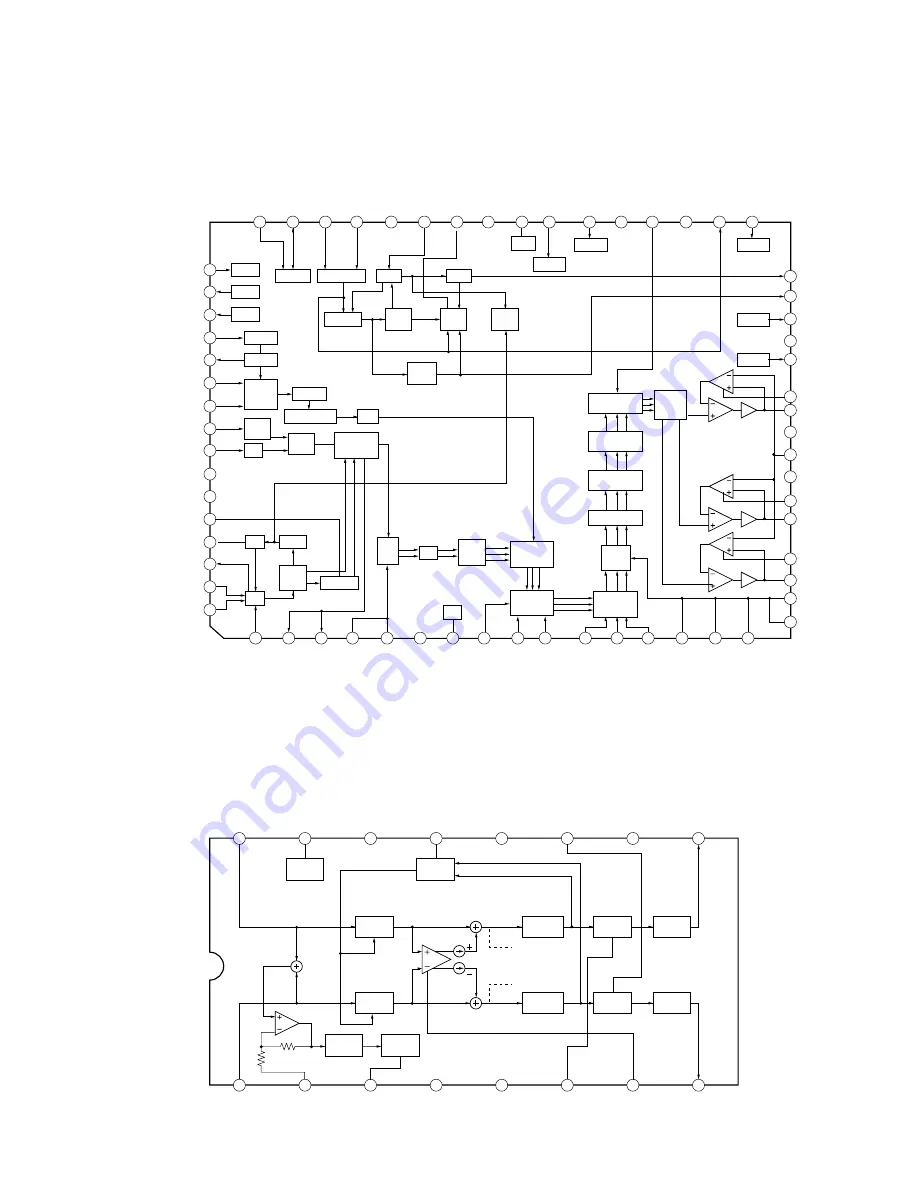

PONRST

LOGIC

SYNCSEPA

HHKILL

DAC

DAC

CLAMP

SYNC

CUT

ACC

DET

50

COMDC

IICBUS

VCO

LOGIC

LOGIC

LOGIC

PWM

REG

1

PLAN

2

R-Y OUT

3

B-Y OUT

4

R-Y IN

5

B-Y IN

6

VCC1

7

VREF

8

R-IN1

9

G-IN1

10

B-IN1

11

R-DET

12

G-DET

13

B-DET

14

R-IN2

15

G-IN2

16

B-IN2

48

SDATA

47

SCLK

46

CSYNC IN

45

NAVI SYNC IN

44

VCC1

43

VCO ADJ

42

AFC DET

41

GND2

40

+BCLKFLT

39

HSYNC LOCK

38

NRGB

37

VSS

36

POL

35

VDIN

34

CSYNC OUT

33

SCP

52

YIN

54

CTRAP IN

55

Y DET

56

ACC DET

ACC

AMP

57

C IN

58

VCC1

59

GND3

60

KILL DET

61

APC DET

62

SC OUT

63

VXO-NTSC

64

VXO-PAL

51

SECAM BLACK ADJ

53

CTRAP OUT

17 YS

18 BLAK

19 B-OUT

20 B-OUT DET

21 G-OUT

22 G-OUT DET

23 GND1

24 VREF DRIV

25 VCC2

26 R-OUT

27 R-OUT DET

28 VCOM OUT

29 VCC3

30 PWM OUT

31 VDOUT

32 HDOUT

R-Y,B-Y

DEMOD

VSYNC

DROP

PHASE

COMP

F

DET

VERT.

COUNT

I/N

SW

BPF

GCA

KILLER

APC

YUV

SW

LOGIC

VXO

GENE

G-Y

GEME

INT/EXT

SW

MATRIX

CLAMP

LIMIT

VXO

REG

DELAY

SHARPNESS

GCA

CONTRAST

GAMMA

INVERT

BRIGHT

OSD

SW

VCOM

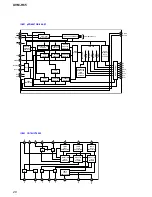

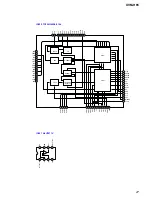

6-9. IC BLOCK DIAGRAMS

IC500 AN2546FH-AV

IC350 TA2061AF

VREF

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

LEVEL

DET

AGC

PRE

EMPHASIS

VCO

BUFFER

AGC

PRE

EMPHASIS

VCO

BUFFER

LIN

VREFC

AGC

AGC-T/C

VCC

FO-R

FO-SW

LOUT

RIN

MIX-NF

AUTO-OFF

GND

FO-L

SURND

ROUT

O.S.M

LEVEL

DET

LOUT=L+K•(L-R)

ROUT=R-K•(L-R)