Trigger modes and appendant registers

Channel Trigger

(c) Spectrum GmbH

99

If you want to set up a two channel board to detect only a positive edge on channel 0, you would have to setup the board like the following

example. Both of the examples either for the single trigger source and the OR trigger mode do not include the necessary settings for the trigger

levels. These settings are detailed described in the following paragraphs.

If you want to set up a two channel board to detect a trigger event on either a positive edge on channel 0 or a negative edge on channel 1

you would have to set up your board as the following example shows.

Channel trigger level

All of the channel trigger modes listed above require at least one trigger level to be set (except SPC_TM_NONE of course). Some modes like

the window triggers require even two levels (upper and lower level) to be set.

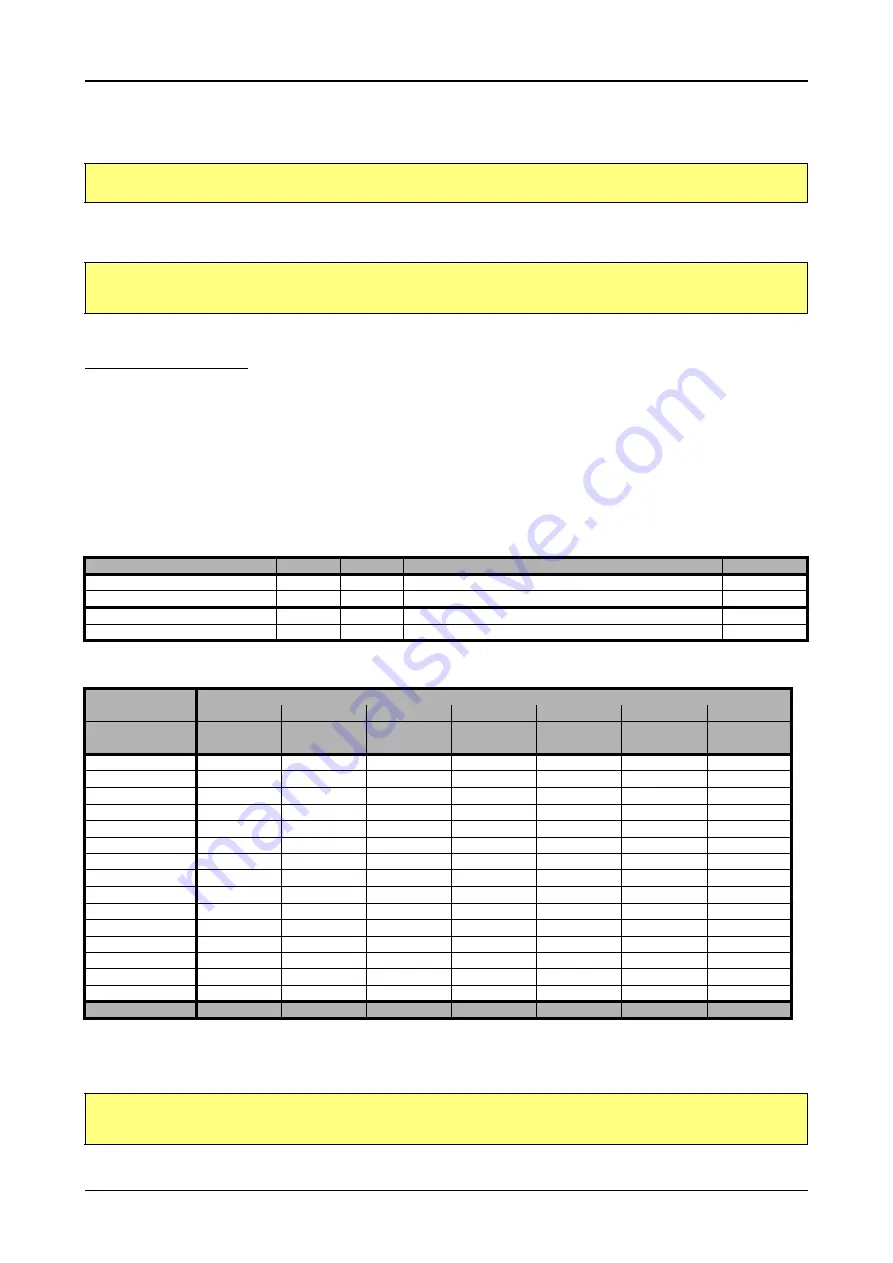

After the data has been sampled, the upper N data bits are compared with the N bits of the trigger levels. The following table shows the level

registers and the possible values they can be set to for your specific card.

As the trigger levels are compared to the digitized data, the trigger levels depend on the channels input range. For every input range available

to your board there is a corresponding range of trigger levels. On the different input ranges the possible stepsize for the trigger levels differs

as well as the maximum and minimum values. The table further below gives you the absolute trigger levels for your specific card series.

10 bit resolution for the trigger levels:

Trigger level representation depending on selected input range

The following example shows, how to set up a one channel board to trigger on channel 0 with rising edge. It is assumed, that the input range

of channel 0 is set to the the ±200 mV range. The decimal value for SPC_TRIG_CH0_LEVEL0 corresponds then with 16.0 mV, which is the

resulting trigger level.

spcm_dwSetParam_i32 (hDrv, SPC_TRIG_CH_ORMASK0, SPC_TMASK0_CH0); // Enable channel 0 in the OR mask

spcm_dwSetParam_i32 (hDrv, SPC_TRIG_CH0_MODE, SPC_TM_POS ); // Set triggermode of channel 0 to positive edge

spcm_dwSetParam_i32 (hDrv, SPC_TRIG_CH_ORMASK0, SPC_TMASK0_CH0 | SPC_TMASK0_CH1); // Enable channel 0 + 1

spcm_dwSetParam_i32 (hDrv, SPC_TRIG_CH0_MODE, SPC_TM_POS ); // Set triggermode of channel 0 to positive edge

spcm_dwSetParam_i32 (hDrv, SPC_TRIG_CH1_MODE, SPC_TM_NEG ); // Set triggermode of channel 1 to negative edge

Register

Value

Direction

Description

Range

SPC_TRIG_CH0_LEVEL0

42200

read/write

Trigger level 0 channel 0: main trigger level / upper level if 2 levels used

-511 to +511

SPC_TRIG_CH1_LEVEL0

42201

read/write

Trigger level 0 channel 1: main trigger level / upper level if 2 levels used

-511 to +511

SPC_TRIG_CH0_LEVEL1

42300

read/write

Trigger level 1 channel 0: auxiliary trigger level / lower level if 2 levels used

-511 to +511

SPC_TRIG_CH1_LEVEL1

42301

read/write

Trigger level 1 channel 1: auxiliary trigger level / lower level if 2 levels used

-511 to +511

Input ranges

Triggerlevel

±200 mV

±500 mV

±1 V

±2 V

±2.5 V

±5 V

±10 V

Path 0 (Buffered)

x

x

x

x

n.a.

x

x

Path 1 (HF, 50 Ohms)

n.a.

x

x

n.a.

x

x

n.a.

511

+199.6 mV

+499.0 mV

+998.0 mV

+1.996 V

+2.495 V

+4.99 V

+9.98 V

510

+199.2 mV

+498.0 mV

+996.0 mV

+1.992 V

+2.490 V

+4.98 V

+9.96 V

…

256

+100.0 mV

+250.0 mV

+500.0 mV

+1.00 V

+1.25 V

+2.50 V

+5.00 V

…

2

+0.8 mV

+2.0 mV

+4.0 mV

+7.8 mV

+9.8 mV

+19.6 mV

+39.0 mV

1

+0.4 mV

+1.0 mV

+2.0 mV

+3.9 mV

+4.9 mV

+9.8 mV

+19.5 mV

0

0 V

0 V

0 V

0 V

0V

0 V

0 V

-1

-0.4 mV

-1.0 mV

-2.0 mV

-3.9 mV

-4.9 mV

-9.8 mV

-19.5 mV

-2

-0.8 mV

-2.0 mV

-4.0 mV

-7.8 mV

-9.8 mV

-19.6 mV

-39.0 mV

…

-256

-100.0 mV

-250.0 mV

-500.0 mV

-1.00 V

-1.25 V

-2.50 V

-5.00 V

…

-510

-199.2 mV

-498.0 mV

-996.0 mV

-1.992 V

-2.490 V

-4.98 V

-9.96 V

-511

-199.6 mV

-499.0 mV

-998.0 mV

-1.996 V

-2.495 V

-4.99 V

-9.98 V

Step size

0.4 mV

1.0 mV

2.0 mV

3.9 mV

4.9 mV

9.8 mV

19.5 mV

spcm_dwSetParam_i32 (hDrv, SPC_TRIG_CH0_MODE, SPC_TM_POS); // Setting up channel trig (rising edge)

spcm_dwSetParam_i32 (hDrv, SPC_TRIG_CH0_LEVEL0, 40); // Sets triggerlevel to 16.0 mV

spcm_dwSetParam_i32 (hDrv, SPC_TRIG_CH_ORMASK0, SPC_TMASK0_CH0); // and enable it within the OR mask