100

M3i.48xx / M3i.48xx-exp Manual

Channel Trigger

Trigger modes and appendant registers

Reading out the number of possible trigger levels

The Spectrum driver also contains a register that holds the value of the maximum possible different trigger levels considering the above men-

tioned exclusion of the most negative possible value. This is useful, as new drivers can also be used with older hardware versions, because

you can check the trigger resolution during run time. The register is shown in the following table:

In case of a board that uses 8 bits for trigger detection the returned value would

be 127, as either the zero and 127 positive and negative values are possi-

ble.The resulting trigger step width in mV can easily be calculated from the re-

turned value. It is assumed that you know the actually selected input range.

To give you an example on how to use this formula we assume, that the

±1.0 V input range is selected and the board uses 8 bits for trigger detection.

The result would be 7.81 mV, which is the step width for your type of board

within the actually chosen input range.

Detailed description of the channel trigger modes

For all channel trigger modes, the OR mask must contain the corresponding input channels (channel 0 taken as example here):

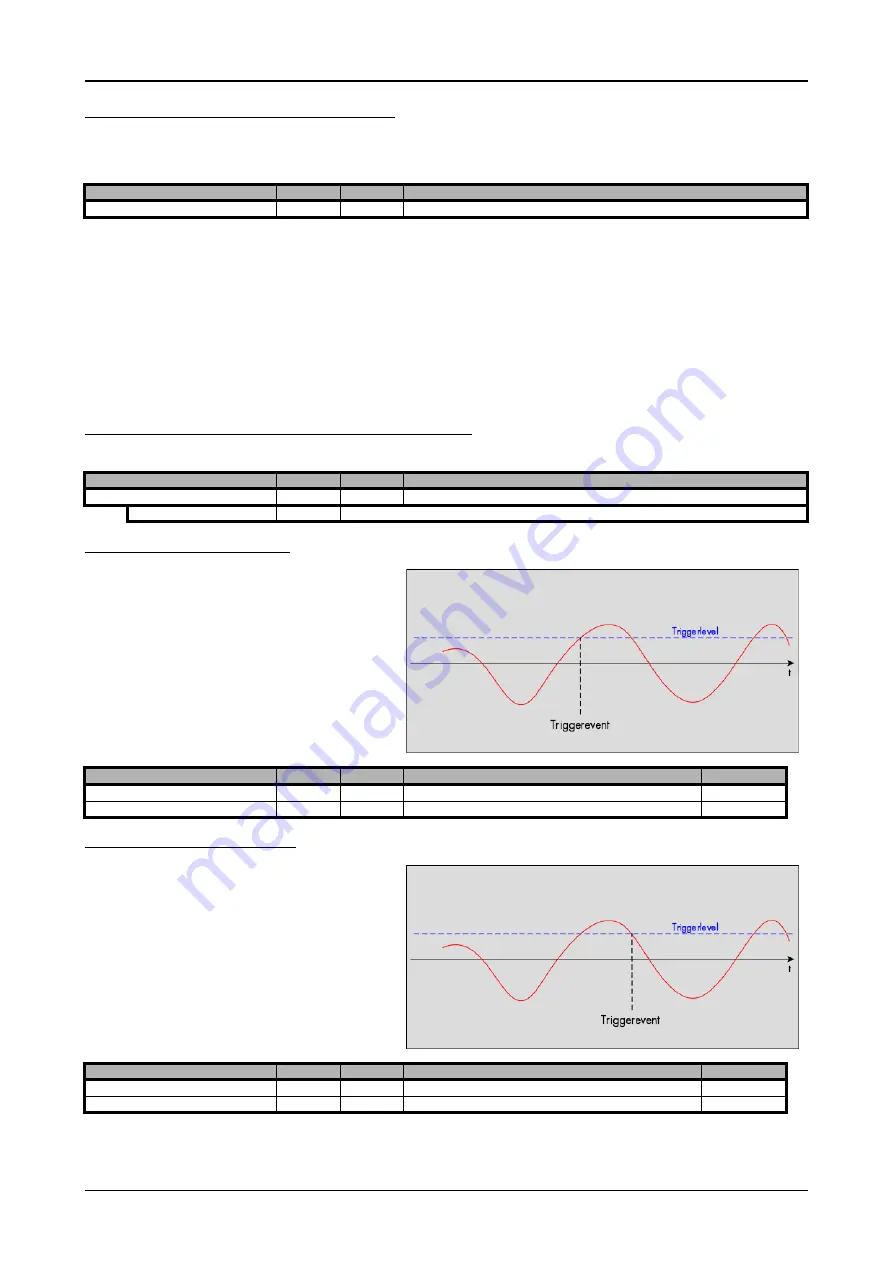

Channel trigger on positive edge

The analog input is continuously sampled with the selected

sample rate. If the programmed trigger level is crossed by

the channel’s signal from lower values to higher values (ris-

ing edge) then the trigger event will be detected.

These edge triggered channel trigger modes correspond to

the trigger possibilities of usual oscilloscopes.

Channel trigger on negative edge

The analog input is continuously sampled with the selected

sample rate. If the programmed trigger level is crossed by

the channel’s signal from higher values to lower values (fall-

ing edge) then the trigger event will be detected.

These edge triggered channel trigger modes correspond to

the trigger possibilities of usual oscilloscopes.

Register

Value

Direction

Description

SPC_READTRGLVLCOUNT

2500

r

Contains the number of different possible trigger levels meaning ± of the value.

Register

Value

Direction

Description

SPC_TRIG_CH_ORMASK0

40460

read/write

Defines the OR mask for the channel trigger sources.

SPC_TMASK0_CH0

1h

Enables channel0 input for the channel OR mask

Register

Value

Direction

set to

Value

SPC_TRIG_CH0_MODE

40610

read/write

SPC_TM_POS

1h

SPC_TRIG_CH0_LEVEL0

42200

read/write

Set it to the desired trigger level relatively to the channel’s input range.

board dependent

Register

Value

Direction

set to

Value

SPC_TRIG_CH0_MODE

40610

read/write

SPC_TM_NEG

2h

SPC_TRIG_CH0_LEVEL0

42200

read/write

Set it to the desired trigger level relatively to the channel’s input range.

board dependent

Trigger step width

Input Range

m

ax

Number of trigger levels

1

+

---------------------------------------------------------------------------------------------------------------------

=

Trigger step width

+1000 mV

127

1

+

---------------------------------------------

=