PCI.212 Manual

31.03.2004

Page 13 of 25

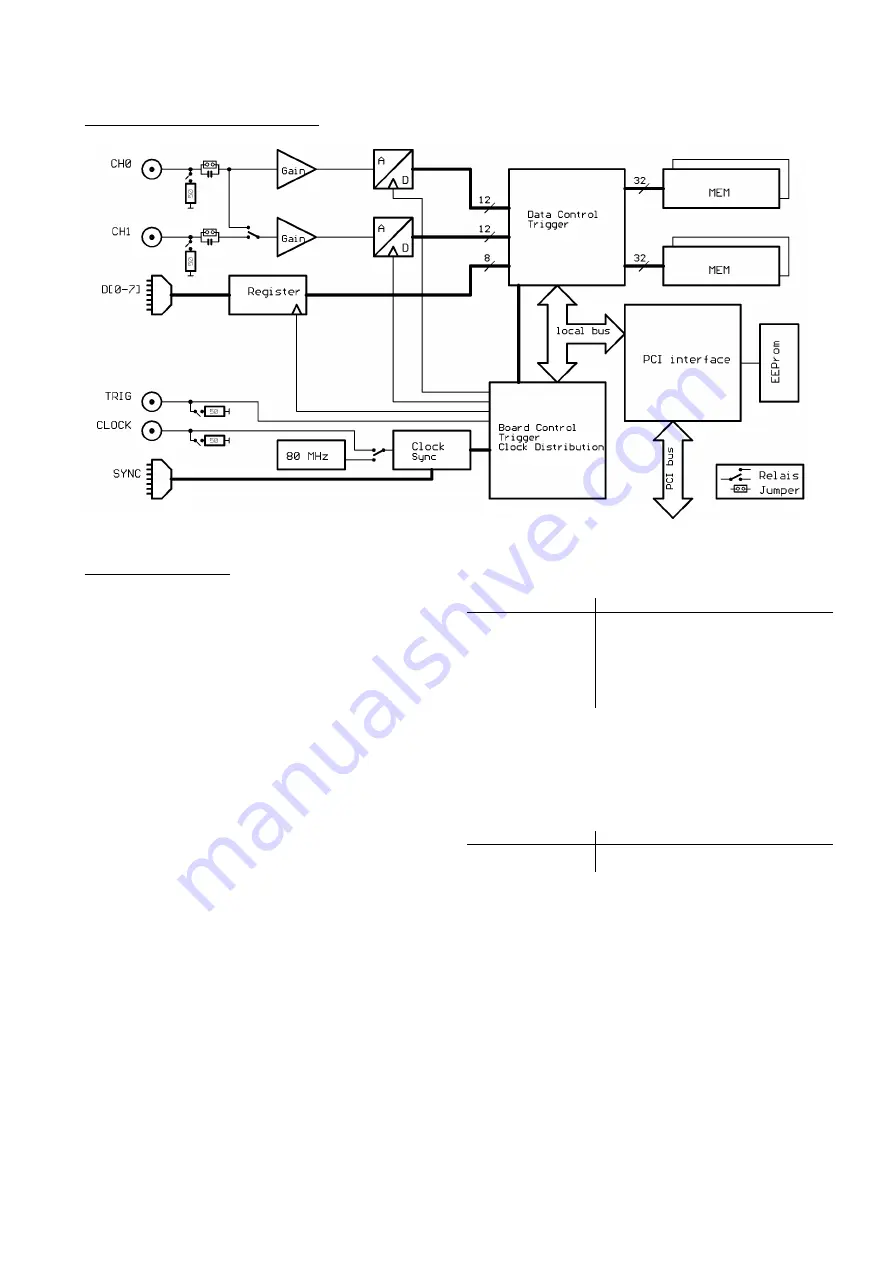

Block diagram PCI.212

Technical data

Resolution

12 bit

Input range

r

250 mV

r

500 mV

r

1 V

r

2 V

Samplerate

312 kHz up to 80 MHz

Offset error (40 MHz)

d

3 LSB

d

2 LSB

d

2 LSB

d

2 LSB

Bandwidth DC 3 dB

0 Hz to 35 MHz

Offset error (80 MHz)

d

4 LSB

d

3 LSB

d

3 LSB

d

3 LSB

Bandwidth AC 3 dB

20 Hz to 35 MHz

Gain error (40 MHz)

d

1 %

d

0.75 %

d

0.5 %

d

0.5 %

Differential linearity error

d

±1 LSB

Gain error (80 MHz)

d

1 %

d

0.75 %

d

0.5 %

d

0.5 %

Integral linearity error

d

±2 LSB

Noise (40 MHz)

d

3 LSB

d

1 LSB

d

1 LSB

d

1 LSB

SFDR fs = 12 MHz

61 dBFS typ.

Noise (80 MHz)

d

4 LSB

d

2 LSB

d

2 LSB

d

2 LSB

ENOB fs=500 kHz fck=40 MHz

10.3 bit typ. (ADC)

Crosstalk (40 MHz)

--64 dB

-65 dB

-68 dB

-69 dB

ENOB fs=12 MHz, fck=40 MHz

10.0 bit typ. (ADC)

Aperture jitter

7 ps rms (ADC)

Dimension (PCI)

312 mm x 107 mm

Input impedance

50 Ohm or 1 MOhm || 25 pF

Connector

9 mm BNC female

Trigger output delay

13 samples

Overvoltage protection

r

20 V

Trigger accuracy

d

40 MHz (80 MHz)

1 sample (2 samples)

Warm up time

10 minutes

Ext. Trigger to data

d

40 MHz (80 MHz)

10 samples (20 samples)

Operating temperatur

0

q

C - 50

q

C

Digital input to analog input delay

0 samples

Storage temperatur

-10

q

C - 70

q

C

Ext. clock: output delay

-20 ns

Humidity

10% to 90% non condensing

Ext. clock: delay to internal clock

30 ns

Sync: board to board trigger jitter

0 samples

+3.3 V

+5 V

+12 V

-12 V

Sync: board to board clock delay

d

1 ns

Power comsumption (A)

0 mA

1700 mA

80 mA

80 mA

Power consumption (W)

0.0 W

8.5 W

0.1 W

0.1 W