Registers

STA309A

38/67

Doc ID 13855 Rev 4

7.2.28

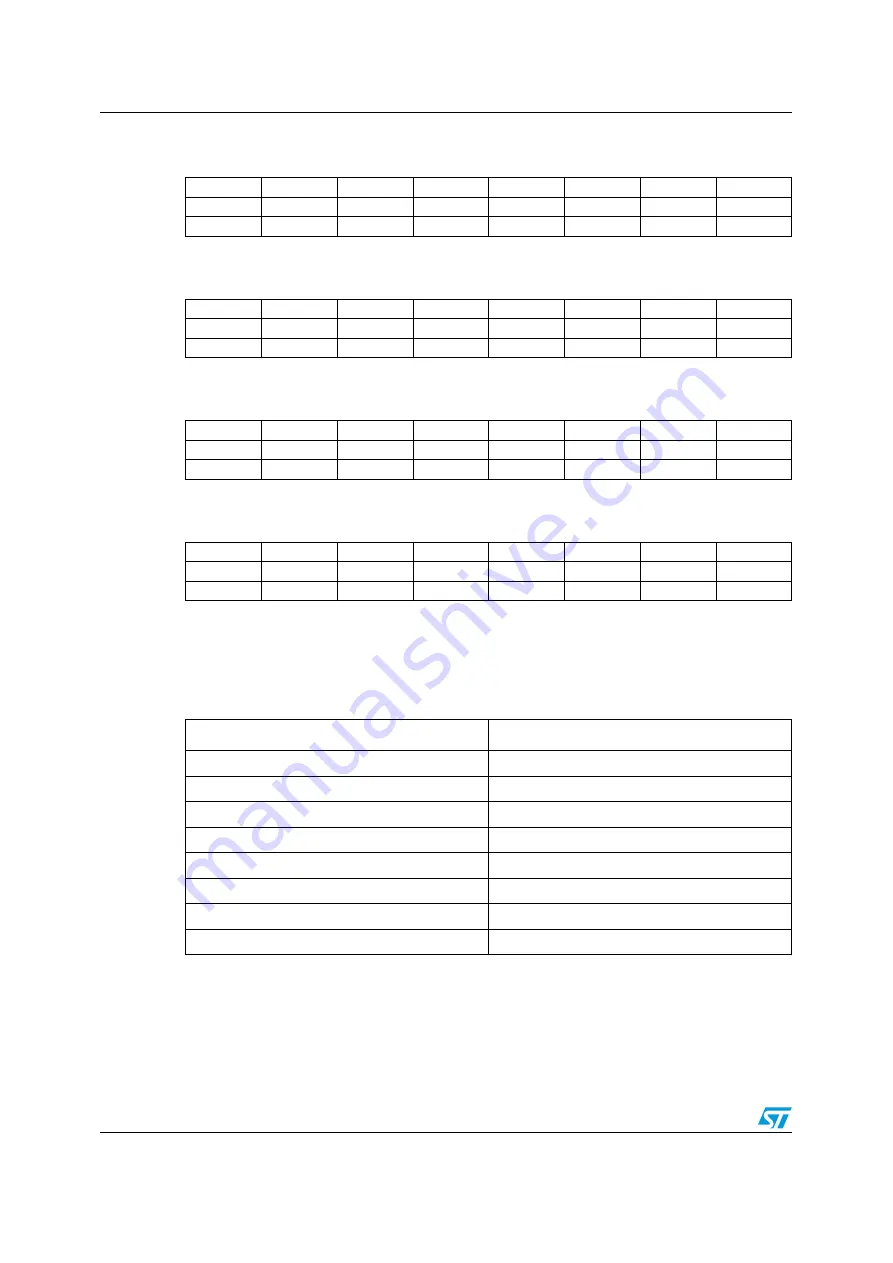

Channel input mapping channels 1 and 2 (0x1B)

7.2.29

Channel input mapping channels 3 and 4 (0x1C)

7.2.30

Channel input mapping channels 5 and 6 (0x1D)

7.2.31

Channel input mapping channels 7 and 8 (0x1E)

Each channel received via I

2

S can be mapped to any internal processing channel via the

channel input mapping registers. This allows for flexibility in processing, simplifies output

stage designs, and enables the ability to perform crossovers. The default settings of these

registers map each I

2

S input channel to its corresponding processing channel.

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

C2IM2

C2IM1

C2IM0

Reserved

C1IM2

C1IM1

C1IM0

0

0

0

1

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

C4IM2

C4IM1

C4IM0

Reserved

C3IM2

C3IM1

C3IM0

0

0

1

1

0

0

1

0

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

C6IM2

C6IM1

C6IM0

Reserved

C5IM2

C5IM1

C5IM0

0

1

0

1

0

1

0

0

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

C8IM2

C8IM1

C8IM0

Reserved

C7IM2

C7IM1

C7IM0

0

1

1

1

0

1

1

0

Table 52.

CnIM bits

CnIM[2:0]

Serial input from

000

Channel 1

001

Channel 2

010

Channel 3

011

Channel 4

100

Channel 5

101

Channel 6

110

Channel 7

111

Channel 8