Registers

STA309A

54/67

Doc ID 13855 Rev 4

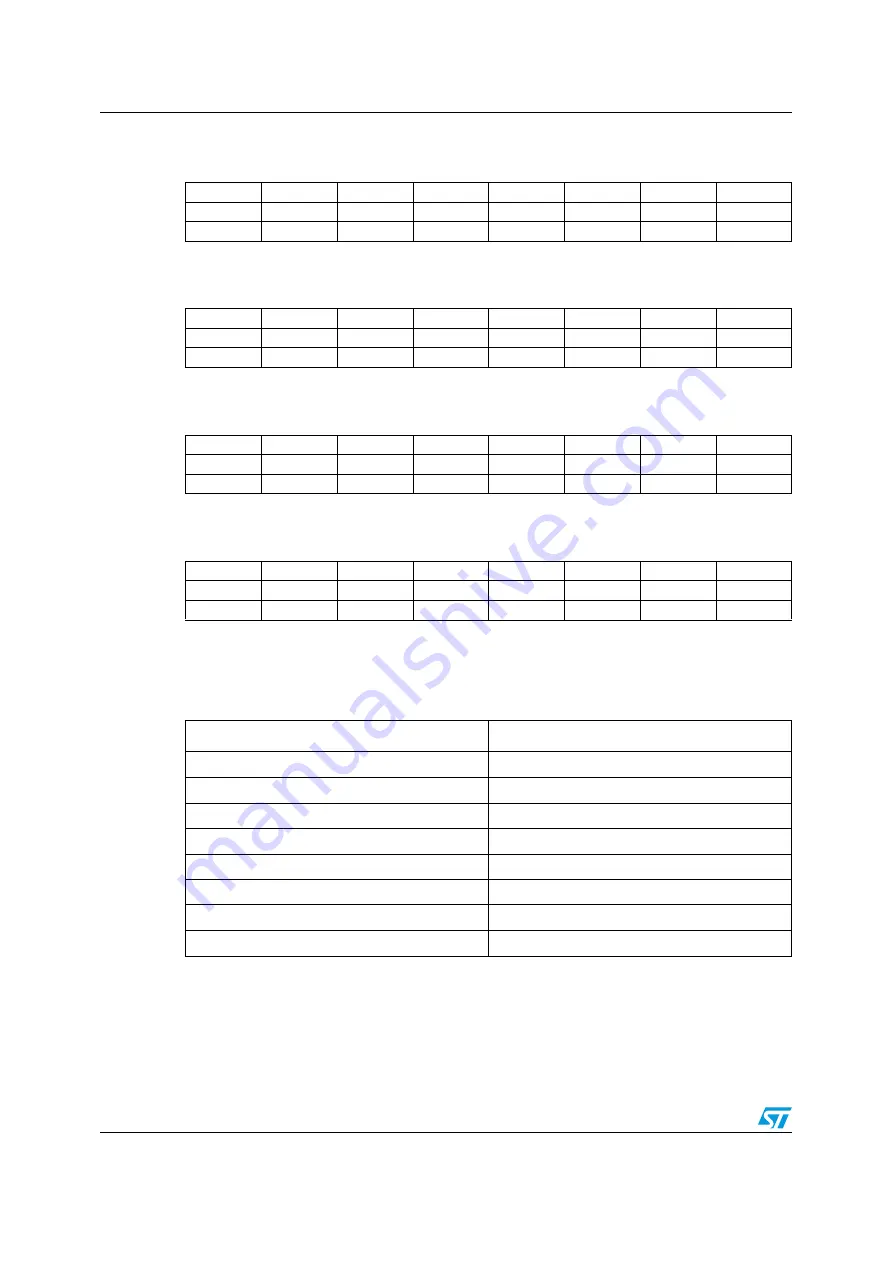

7.2.57 Channel

I

2

S output mapping channels 1 and 2 (0x37)

7.2.58 Channel

I

2

S output mapping channels 3 and 4 (0x38)

7.2.59 Channel

I

2

S output mapping channels 5 and 6 (0x39)

7.2.60 Channel

I

2

S output mapping channels 7 and 8 (0x3A)

Each I

2

S output channel can receive data from any channel output of the volume block.

Which channel a particular I

2

S output receives is dependent upon that channels CnOM

register bits.

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

C2OM2

C2OM1

C2OM0

Reserved

C1OM2

C1OM1

C1OM0

0

0

0

1

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

C4OM2

C4OM1

C4OM0

Reserved

C3OM2

C3OM1

C3OM0

0

0

1

1

0

0

1

0

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

C6OM2

C6OM1

C6OM0

Reserved

C5OM2

C5OM1

C5OM0

0

1

0

1

0

1

0

0

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

C8OM2

C8M1

C8OM0

Reserved

C7OM2

C7OM1

C7OM0

0

1

1

1

0

1

1

0

Table 79.

CnOM serial output

CnOM[2:0]

Serial output from

000

Channel 1

001

Channel 2

010

Channel 3

011

Channel 4

100

Channel 5

101

Channel 6

110

Channel 7

111

Channel 8