STA309A

Registers

Doc ID 13855 Rev 4

55/67

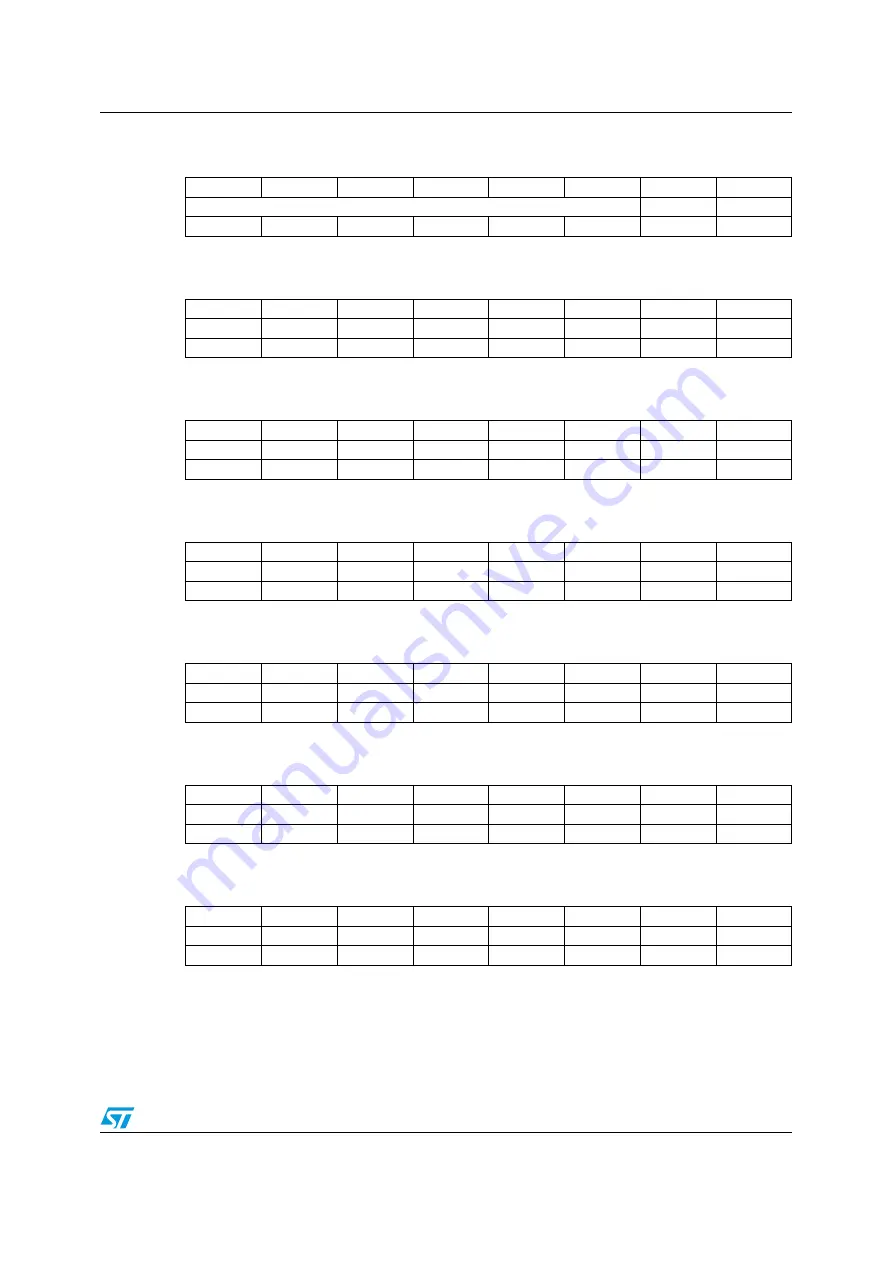

7.2.61 Coefficient

address register 1 (0x3B)

7.2.62 Coefficient

address register 2 (0x3C)

7.2.63 Coefficient

b1

data

register, bits 23:16 (0x3D)

7.2.64 Coefficient

b1

data

register, bits 15:8 (0x3E)

7.2.65 Coefficient

b1

data

register, bits 7:0 (0x3F)

7.2.66 Coefficient

b2

data

register, bits 23:16 (0x40)

7.2.67 Coefficient

b2

data

register, bits 15:8 (0x41)

D7

D6

D5

D4

D3

D2

D1

D0

Reserved

CFA9

CFA8

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

CFA7

CFA6

CFA5

CFA4

CFA3

CFA2

CFA1

CFA0

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

C1B23

C1B22

C1B21

C1B20

C1B19

C1B18

C1B17

C1B16

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

C1B15

C1B14

C1B13

C1B12

C1B11

C1B10

C1B9

C1B8

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

C1B7

C1B6

C1B5

C1B4

C1B3

C1B2

C1B1

C1B0

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

C2B23

C2B22

C2B21

C2B20

C2B19

C2B18

C2B17

C2B16

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

C2B15

C2B14

C2B13

C2B12

C2B11

C2B10

C2B9

C2B8

0

0

0

0

0

0

0

0