STA309A

Pin description

Doc ID 13855 Rev 4

15/67

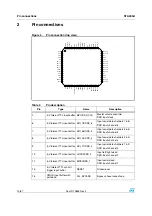

4 Pin

description

Master volume override (MVO)

This pin enables the user to bypass the volume control on all channels. When MVO is pulled

high, the master volume register is set to 0x00, which corresponds to its full scale setting.

The master volume register setting offsets the individual channel volume settings, which

default to 0 dB.

Serial data in (SDI_12, SDI_34, SDI_56, SDI_78)

Audio information enters the device here. Six format choices are available including I

2

S,

left- or right-justified, LSB or MSB first, with word widths of 16, 18, 20 and 24 bits.

RESET

Driving this pin low turns off the outputs and returns all settings to their defaults.

I

2

C bus

The SA, SDA and SCL pins operate per the Phillips I

2

C specification. See Section 5.

Phase locked loop (PLL)

The phase locked loop section provides the system timing signals and CKOUT.

Clock output (CKOUT)

System synchronization and master clocks are provided by the CKOUT.

PWM outputs (OUT1 through OUT8)

The PWM outputs provide the input signal for the power devices.

External amplifier power-down (EAPD)

This signal can be used to control the power-down of DDX power devices.

Serial data out (SDO_12, SDO_34, SDO_56, SDO_78)

These are the outputs for audio information. Six different formats are available including I

2

S,

left- or right-justified, LSB or MSB first, with word widths of 16, 18, 20 and 24 bits.

Device power-down (PWDN)

Pulling PWDN low begins the power-down sequence which puts the STA309A into a

low-power state. EAPD (pin 51) goes low approximately 30 ms later.