10

SME5224AUPA-400

400 MHz CPU, 4.0 MB E-Cache

UltraSPARC

™

-II CPU Module

July 1999

Sun Microsystems, Inc

.

LOW VOLTAGE PECL

Two trace signals compose each clock: one positive signal and one negative signal. Each signal is 180-degrees

out of phase with the other. Signal timing is referenced to when the positive LVPECL signal transitions from

low to high at the cross-over point, when the negative signal transitions from high to low. The trace-pair are

routed side-by-side and use parallel termination, (specific routing techniques are require).

CPU CLOCK INPUT

The PLL in the CPU doubles the clock frequency presented at its clock pin. So, for a 400 MHz core CPU clock

frequency, the CPU_CLK signal is 200 MHz. Therefore, for the CPU, actions will appear to occur at both tran-

sitions of the input CPU_CLK.

CLOCK TRACE DELAYS

The LVPECL propagation time is constant for all clock signals so all balancing is based on length rather than

time. All LVPECL traces are striplines (dielectric and power planes top and bottom) with a fixed 180 ps per

inch propagation time using the FR4, PCB Dielectric.

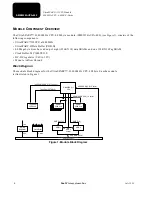

Clock Buffer

SRAM

SRAM

SRAM

SRAM

SRAM

SRAM

SRAM

SRAM

UDB-II

SRAM/TAG

UltraSPARC-II

CPU

Clock

Buffer

Clock

Divider

CPU_CLK

UPA_CLK0

UPA_CLK1

UPA_CLK2

UPA_CLKx

UPA_CLK

UPA Device

Module

Connector

Module Boundary

Clock

Generator

UDB-II

UPA Device

Serial

Parallel

Figure 3. Clock Signal Distribution