16

A+ Server AS -2114GT-DNR User's Manual

Note:

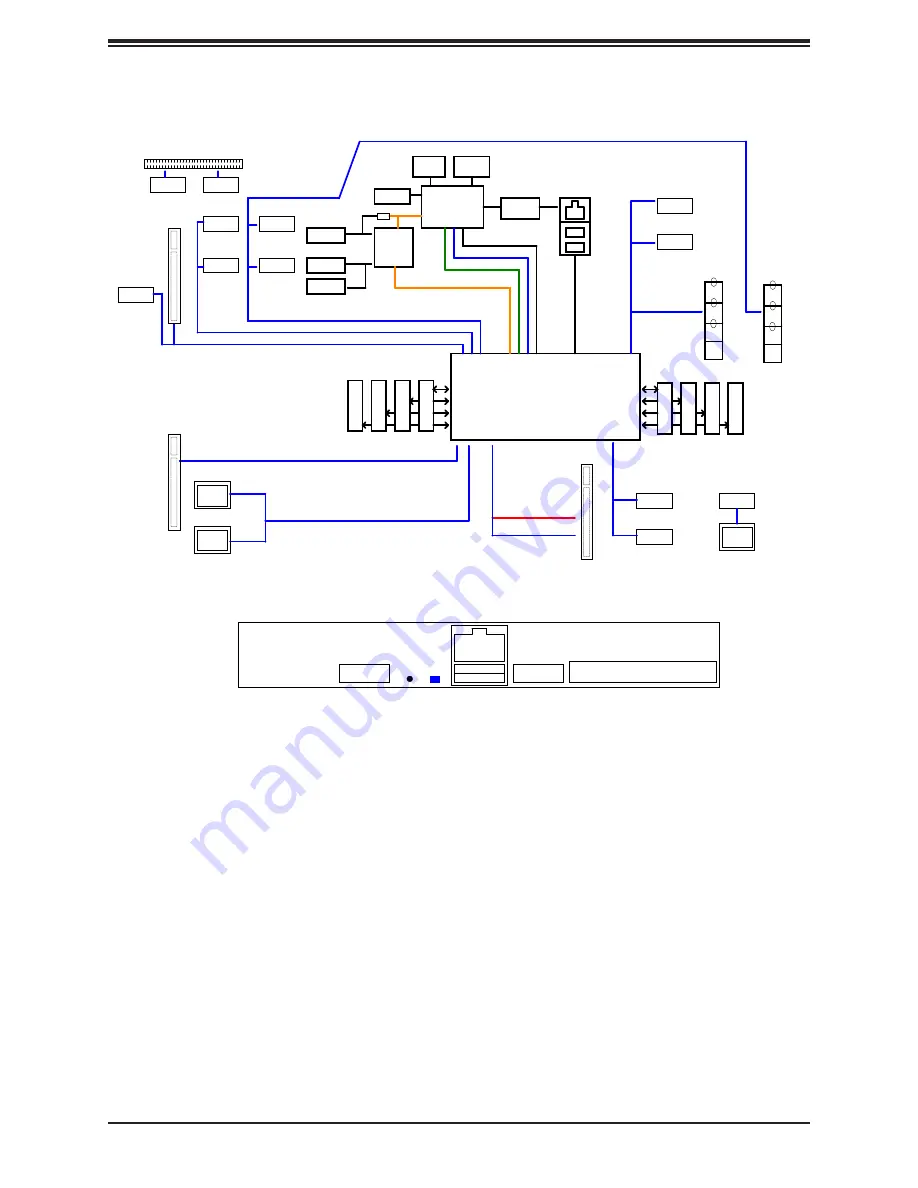

This is a general block diagram and may not exactly represent the features on your

motherboard. See the previous pages for the actual specifications of your motherboard.

Figure 1-6. Chipset Block Diagram

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

H12SSG-AN6 AMD SP3 Rome Rev. 1.00

Rear I/O

01 Block Diagram------- SSW-NTL

02 SMBus Diagram------- SSW-NTL

03 Power Rail Diagram-- SSW-NTL

04 Clock Tree Diagram-- SSW-NTL

05 Reset Diagram------- SSW-NTL

06 P0-MEM_CH_A_B------- SSW-NTL

07 P0-MEM_CH_C_D------- SSW-NTL

08 P0-MEM_CH_E_F------- SSW-NTL

09 P0-MEM_CH_G_H------- SSW-NTL

10 P0-DIMM-CH-A-------- SSW-NTL

11 P0-DIMM-CH-B-------- SSW-NTL

12 P0-DIMM-CH-C-------- SSW-NTL

13 P0-DIMM-CH-D-------- SSW-NTL

14 P0-DIMM-CH-E-------- SSW-NTL

15 P0-DIMM-CH-F-------- SSW-NTL

16 P0-DIMM-CH-G-------- SSW-NTL

17 P0-DIMM-CH-H-------- SSW-NTL

18 P0-PCIe & SATA & GOP -------- SSW-NTL + AN6

19 P0-PCIe & SATA -------- SSW-NTL + AN6

20 P0-USB & LPC & UART -------- SSW-NTL + AN6

21 P0-CLK/RESET/SPI/SMB -------- SSW-NTL + AN6

22 P0-SVID/WAFL/JTAG -------- SSW-NTL + AN6

23 P0-POWER----------- SSW-NTL + AN6

24 P0-GROUND---------- SSW-NTL

25 P0 BYPASS CAP

26 P0-DIMM-BYPASS-CAP

27 P0-HW-STRAPs----------------- SSW-NTL + AN6

28 P0-CLOCK BUFF-------X12DDW

29 Blank (SATA)

30 Blank (USB)

31 USB Rear I/O ------ SSW-NTL

32 PCI-E CPU0 P0&P1_LUIO

33 Blank (PCIe)

34 PCI-E CPU0 P2_OCP

35 PCI-E CPU0 P3_SlimSAS

36 PCI-E CPU0 G0&G1_RUIO

37 Blank (PCIe)

38 PCI-E CPU0 G2A&G2B_Impel

39 PCI-E CPU0 G2C&G2D_M2A/M2B

40 PCI-E CPU0 G3_RUIO

41 FAN & RT1 & RT2 ------ SSW-NTL

42 Front Panlel ------ SSW-NTL

43 HDT ------ SSW-NTL +AN6

44 CPLD ------ AN6 + H12DGO

45 PCIe Reset

46 SMBus ------ SSW-NTL + AN6

47 BMC TPM/INTRUDER/VGA ------ SSW-NTL + AN6

48 BMC AST2600 DDR4/ESPI/SMB ----- to AN6 p.48

49 BMC AST2600 SPI/UART/MAC ----- to AN6 p.49

50 BMC AST2600 VGA/FAN/ADC/USB ----- to AN6 p.50

51 BMC AST2600 POWER/GND ----- to AN6 p.51

52 BMC- BMC EXRST/RSMRST ----- to AN6 p.52

53 Blank (NCSI) ----- to AN6 p.53

54 BMC VOLTAGE RAGULATOR ----- to AN6 p.54

55 BMC LAN RTL8211F-CG ----- to AN6 p.55

56 BMC- COM & ROM & SD ----- to AN6 p.56

57 Blank

58 P0_VDDCR_CPU_RUN VRM ----- to SST-PS p.58

59 P0_VDDCR_CPU_RUN Phase 1-3 ----- to SST-PS p.59

60 P0_VDDCR_CPU_RUN Phase 5-7 ----- to SST-PS p.60

61 P0_VDDCR_SOC_RUN VRM ----- to SST-PS p.61

62 P0_VDDCR_SOC_RUN Stage ----- to SST-PS p.62

63 P0 ABCD VDDIO_VPP VRM ----- to SST-PS p.63

64 P0 ABCD VDDIO Stage ----- to SST-PS p.64

65 P0 ABCD VPP ------ X12DDW, p.71

66 P0 EFGH VDDIO VRM ----- to SST-PS p.66

67 P0 EFGH VDDIO Stage ----- to SST-PS p.67

68 P0 EFGH VPP ------ X12DDW, p.71

69 P0 VTT ------ to SSW-NTL p.68, 69.

70 P0 VDD1.8 RUN & DUAL ------ to SSW-NTL p.70

71 P0 SOC DUAL ------ to SSW-NTL p.71

72 Blank

73 POWER CONNECTOR

74 HOT SWAP CONTROLLER ------ from X12DGO-6, P.95

75 12V DUAL Control ------ from H12DGO-6, P.107

76 +VDD_5_DUAL ------ from H12DGO-6, p.107

77 +VDD_33_DUAL ------ from x12DDW-6, p.74

78 +VDD_5_RUN ------ New

79 +VDD_33_RUN ------- to H12DSG-CPU, p.110

80 OCP ISOLATION

81 OCP POWER

82 Manual Parts

83 History

USB1_HSD[2:3]

+ USB1_SS[2:3]

USB_0_HSD[0,1]

CPU WAFL [1]

JMP3

SPI

CPU

BMC ROM

CPU G1 [15:0]

CPU P1 [15:0]

CPU G0 [15:0]

VGA

VGA

BMC

AST2600

JSXB1

Impel

x8

CPU P3 [15:0]

LPC

CPU G0 [15:8]

PHY

RTL8211F

CPU G3 [15:8]

Dedicated

LAN

USB3.0

EPYC Processor (AMD Socket SP3)

UID

LED

SPI

CPLD

M.2 Conn

M key

BIOS ROM

TPM

JAIOM1

DDR4

COM1

HEADER

CPU G3 PCIe[7:0] / SATA[37:30]

CPU P0 [15:0]

UID

BTN

Rear

2X

USB 3.0

IPMI LAN

RJ45

A

J3

B

DD

R4

D

IM

M

J4

J1

C

DD

R4

D

IM

M

DD

R4

D

IM

M

J2

D

DD

R4

D

IM

M

J8

J5

F

DD

R4

D

IM

M

J6

G

DD

R4

D

IM

M

DD

R4

D

IM

M

DD

R4

D

IM

M

E

J7

H

Slim SAS

x4

Slim SAS

x8

Slim SAS

x8

CPU P1 [15:8]

CPU P1 [7:4]

JPCIE1

JPCIE2

CPU P2 [15:0]

CPU P3 [11:8]

CPU P3 [7:0]

JPCIE5

JPCIE6

CPU G0 [7:0]

JSXB2

JSXB3

JM2A

JM2B

AIOM

USB3.0

JPCIE_ED1

Slim SAS

x8

Slim SAS

x8

[7:0]

[15:8]

Slim SAS

x9

JPCIE_ED2

JPCIE8

JPCIE9

Slim SAS

x9

Slim SAS

x9

CPU P2 [15:8]

CPU P2 [7:0]

JPCIE3

JPCIE4

Slim SAS

x8

Slim SAS

x4

JPCIE7

CPU P0 [7:0]

Slim SAS

x8

CPU P0 [15:8]

JPCIE10

JPCIE11

CPU G2 [15:8]

Slim SAS

x8

CPU G2 [7:0]

Slim SAS

x8

Slim SAS

x8

JPCIE_ED3

[7:0]

COM

CPU P3 [15:12]

CPU P1 [3:0]

Title

Size

Document Number

Rev

Date:

Sheet

of

UPER

S

®

980 Rock Ave., San Jose CA, 95131

TEL : (408) 503-8000

CONFIDENTIAL - DO NOT DUPLICATE

H12SSG-AN6

1.00

Block Diagram

Custom

1

84

Title

Size

Document Number

Rev

Date:

Sheet

of

UPER

S

®

980 Rock Ave., San Jose CA, 95131

TEL : (408) 503-8000

CONFIDENTIAL - DO NOT DUPLICATE

H12SSG-AN6

1.00

Block Diagram

Custom

1

84

Title

Size

Document Number

Rev

Date:

Sheet

of

UPER

S

®

980 Rock Ave., San Jose CA, 95131

TEL : (408) 503-8000

CONFIDENTIAL - DO NOT DUPLICATE

H12SSG-AN6

1.00

Block Diagram

Custom

1

84

Chipset Block Diagram