5-9

Chapter 5: BIOS

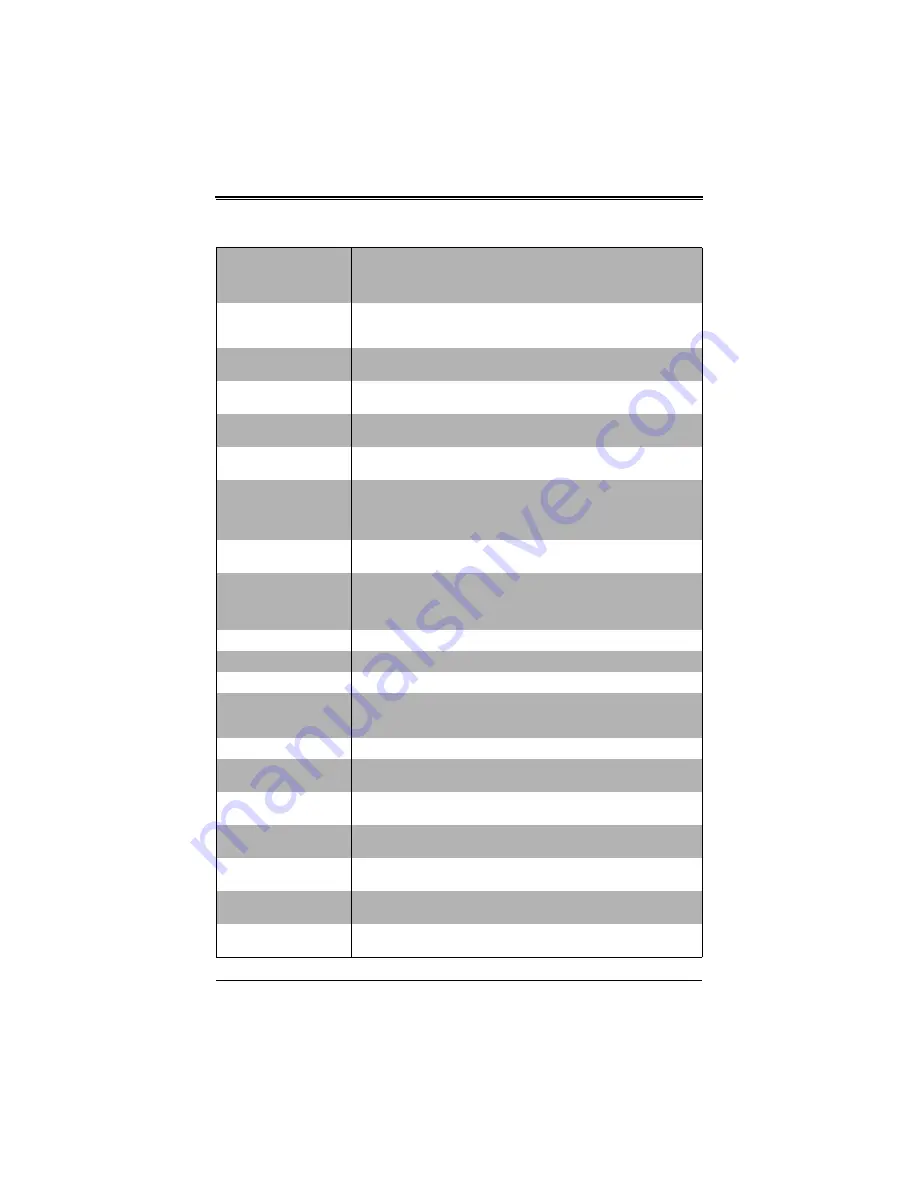

tCCD_L Relaxation

Use this setting to specify if the tCCD_L is overridden by the SPD or based

on the memory frequency. Options include

Auto

, Disable and Enable.

RD2WR Timing

Override

If enabled, the RD2WR Timing is overridden by optimized value. If Auto,

the override only applies ti Samsung’s DIMM. Options include Auto,

Disable

and Enable.

Enable ADR

This setting enables the detecting and enabling of ADR. Options include

Enable or

Disable

.

2x Refresh Mode

This setting enables or disables 2x Refresh Mode. Options include

Disable,

Enable for Warm or Hot

and Enable for Hot only.

Memory Topology

This submenu, when selected, provides with you with static information for

memory topology.

Memory RAS

Configuration

This submenu displays and provides options to change the Memory RAS

settings.

Mirror Mode

Mirror Mode will set the entire 1LM/2LM memory in the system to be

mirrored, consequently reducing the memory capacity by half. Options

include

Disable

, Mirror Mode 1LM and Mirror Mode 2LM.

Note:

Mirror Enable will disable XPT Prrefetch.

Memory Rank

Sparing

This setting will Enable or

Disable

Memory Rank Sparing for your system.

Correctable Error

Threshold

Use this setting to set a threshold value from 1 ~32767 for the Correctable

Error Threshold used for sparing, tagging and leaky bucket. Use the + or -

keys on your numpad to toggle up or down a value or type in a number

value for the field for this setting. Default value is

10

.

SDDC

This value Enables or

Disables

SDDC for your system.

ADDDC Sparing

This value Enables or

Disables

ADDDC Sparing for your system.

Patrol Scrub

This setting

Enables

or Disables Patrol Scrub in your system.

Patrol Scrub

Interval

This setting selects the number of hours (1-24) required to complete full

scrub. A value of 0 means auto. Default is

24

. Settings are increased or

decreased using the “

+

” or “

-

” keys on your keyboard’s number pad.

IIO Configuration

This sub-menu configures Integrated I/O Configuration.

EV DFX Features

This setting gives you the option to allow DFX Lock Bits to remain clear or

not. Options include Enable or

Disable

.

CPU1

Configuration

This submenu allows you to configure CPU1 configuration options.

IOU0 (IIO PCIe

Br1)

This setting selects the PCIe port bifurcation for Br1. Options include

x4x4x4x4, x4x4x8, x8x4x4, x8x8, x16 or

Auto

.

IOU1 (IIO PCIe

Br2)

This setting selects the PCIe port bifurcation for Br2. Options include

x4x4x4x4, x4x4x8, x8x4x4, x8x8, x16 or

Auto

.

IOU2 (IIO PCIe

Br3)

This setting selects the PCIe port bifurcation for Br3. Options include

x4x4x4x4, x4x4x8, x8x4x4, x8x8, x16 or

Auto

.

MCP0 (IIO PCIe

Br4)

This setting selects the PCIe port bifurcation for Br4. Options include x16

or

Auto

.

Table 5-5. Chipset Configuration Sub-menu (Continued)

Menu Option

Description

Summary of Contents for SuperBlade SBI-6419P-C3N

Page 1: ...SBI 6419P C3N SuperBlade Module User s Manual Revison 1 0 ...

Page 4: ...SBI 6419P C3N SuperBlade Module User s Manual iv ...

Page 8: ...SBI 6419P C3N SuperBlade Module User s Manual viii Notes ...

Page 30: ...SBI 6419P C3N SuperBlade Module User s Manual 2 18 ...

Page 33: ...3 3 Chapter 3 Setup and Installation Figure 3 1 Inserting a Blade into the Enclosure ...

Page 51: ...SBI 6419P C3N SuperBlade Module User s Manual 3 21 Notes ...

Page 52: ...SBI 6419P C3N SuperBlade Module User s Manual 3 22 ...

Page 79: ...5 19 Chapter 5 BIOS 5 7 IPMI Setup Figure 5 4 IPMI Setup Screen ...

Page 96: ...SBI 6419P C3N SuperBlade Module User s Manual A 10 ...