16

Chapter 1: Introduction

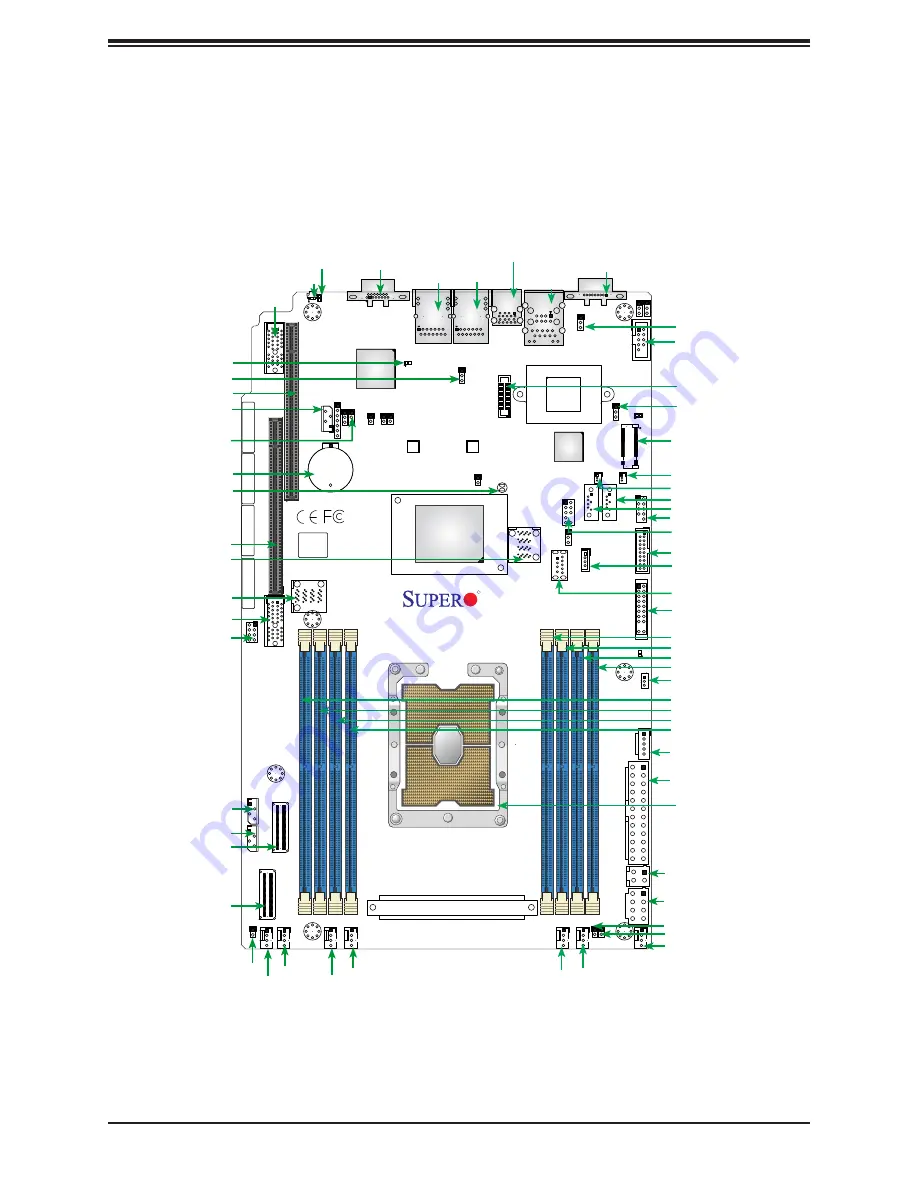

Figure 1-6. Motherboard Layout

1.4 Motherboard Layout

Below is a layout of the X12SPW-TF motherboard with jumper, connector, and LED locations

shown. See the table on the following page for descriptions. For detailed descriptions, pinout

information and jumper settings, refer to Chapter 4 or the

BIOS

LICENSE

1

BAR CODE

IPMI CODE

MAC CODE

SAN MAC

DESIGNED IN USA

X12SPW-TF/F

REV: 2.00

JNCSI1

S-SGPIO1

JBT1

JPWR2

JSD2

JSD1

S-SA

TA1

S-SA

TA0

JSTBY1

JRK1

JPWR3

JPWR1

JF1

JVRM2

JVRM1

JPFR3

JPFR2

JPFR1

JL1

JD1

JPRG1

JWD1

JP4

FAN6

FAN7

FAN4

FAN3

FAN5

FAN1

BT1

NVME0/1

NVME2/3

MH16

MH15

JPI2C1

JIPMB1

JNVI2C

JI2C_EXP1

MH4

MH6

MH1

MH9

MH5

MH3

MH2

JPME1

JPL2

JMP2

JMP1

JPL1

JPL3

SXB2: PCI-E 4.0 X16

SXB1A

SXB1B: PCI-E 4.0 X16 + X16

SXB1C

COM2

I-SATA4~7

M.2-H

COM1

DIMMG1

DIMMH1

DIMME1

DIMMF1

DIMMA1 DIMMB1

DIMMD1

DIMMC1

CPU

USB6/7(3.0)

USB4/5 (3.0)

USB2/3

LAN2

LAN1

CMOS CLEAR

I-SATA0~3

TPM/POR

T80

UID-SW

UID-LED

VGA

USB0/1

IPMI_LAN

USB8(3.0)

LE3

LEDBMC

LE4

FAN2

DIMMC1

DIMMD1

DIMMA1

DIMMB1

DIMMF1

DIMME1

DIMMH1

DIMMG1

COM2

JPWR2

JL1

FAN7

SXB1A

VGA

LAN2 LAN1

USB4/5 (3.0)

IPMI_LAN COM1

JVRM1

JVRM2

FAN1

CPU

UID-LED

UID-SW

USB0/1

JNCSI1

M.2-H

JSD1

JSD2

S-SATA0

S-SATA1

USB2/3

TPM/PORT80

JRK1

USB6/7(3.0)

USB8(3.0)

JF1

JSTBY1

JPI2C1

JPWR3

JPWR1

SXB2

SXB1B

LEDBMC

JIPMB1

JPME1

I-SATA0~3

SXB1C

S-SGPIO1

JNVI2C

J I2C_EXP1

NVME2/3

FAN6

FAN5 FAN4

FAN3 FAN2

NVME0/1

I-SATA4~7

JPL1

JPL3

JPL2

BT1

JBT1