1-15-2

W3N4HTI

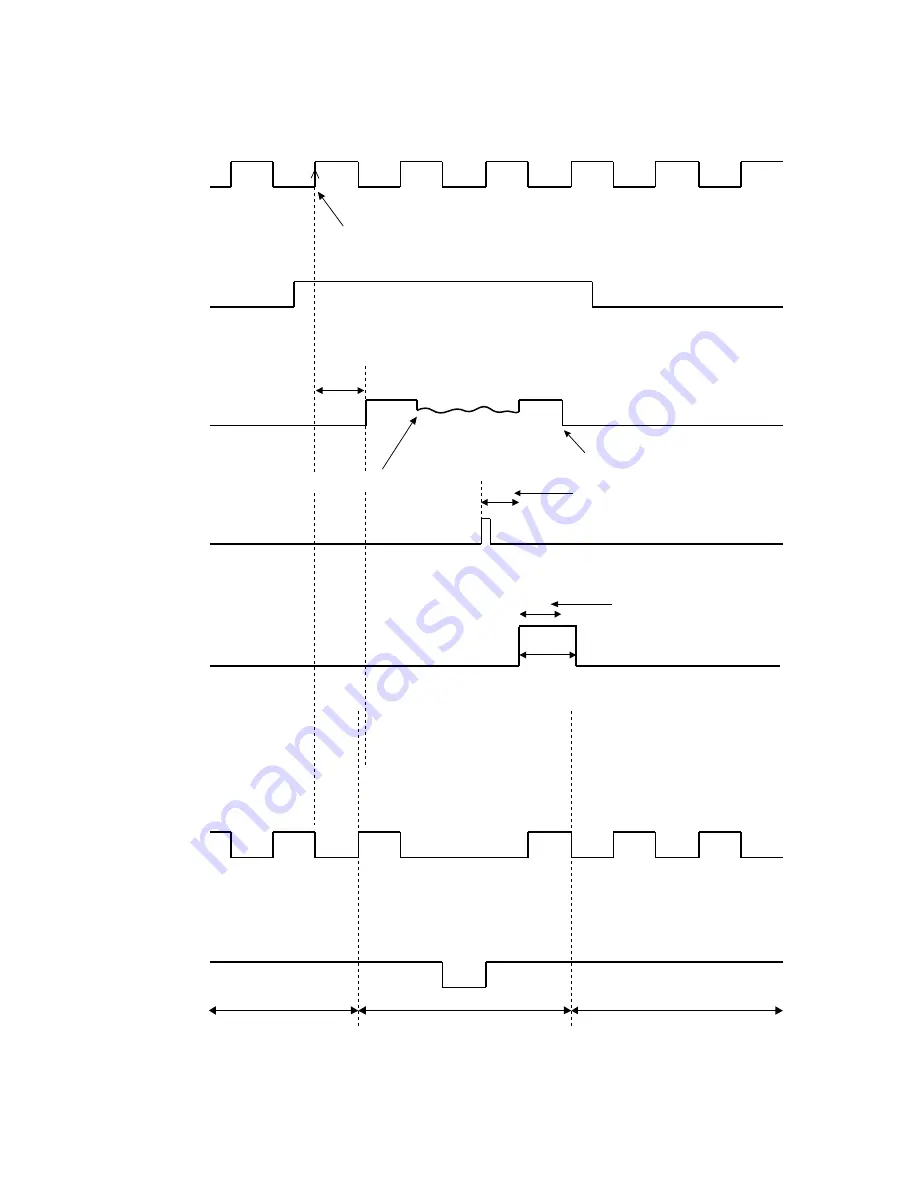

Still/Slow Control Frame Advance Timing Chart

1) SP Mode

Fig. 1

23 RF-SW

F-AD

(Internal Signal)

C-DRIVE

PB CTL

32 C-F/R

99 H-A-SW

98 C-ROTA

The first rise of RF-SW after a rise in F-AD signal

Acceleration Detection (T1)

AT

"H"

"Z"

"H"

"L"

"L"

Stop detection (T2)

ST

Slow Tracking Value

BL

Reversal Limit Value

STILL

FRAME ADVANCE

STILL

20ms

Summary of Contents for DVR90VG

Page 37: ...1 12 3 Main 1 7 Schematic Diagram VCR Section E9A10SCM1 ...

Page 39: ...1 12 5 Main 3 7 Schematic Diagram VCR Section E9A10SCM3 ...

Page 40: ...1 12 6 Main 4 7 Schematic Diagram VCR Section E9A10SCM4 ...

Page 41: ...1 12 7 Main 5 7 Schematic Diagram VCR Section E9A10SCM5 ...

Page 42: ...1 12 8 Main 6 7 Schematic Diagram VCR Section E9A10SCM6 ...

Page 43: ...1 12 9 Main 7 7 Schematic Diagram VCR Section E9A10SCM7 ...

Page 45: ...1 12 11 Front Jack Schematic Diagram VCR Section E9A10SCJK ...

Page 83: ...DVR90VG E9A10UD 2006 04 03 ...