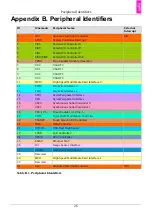

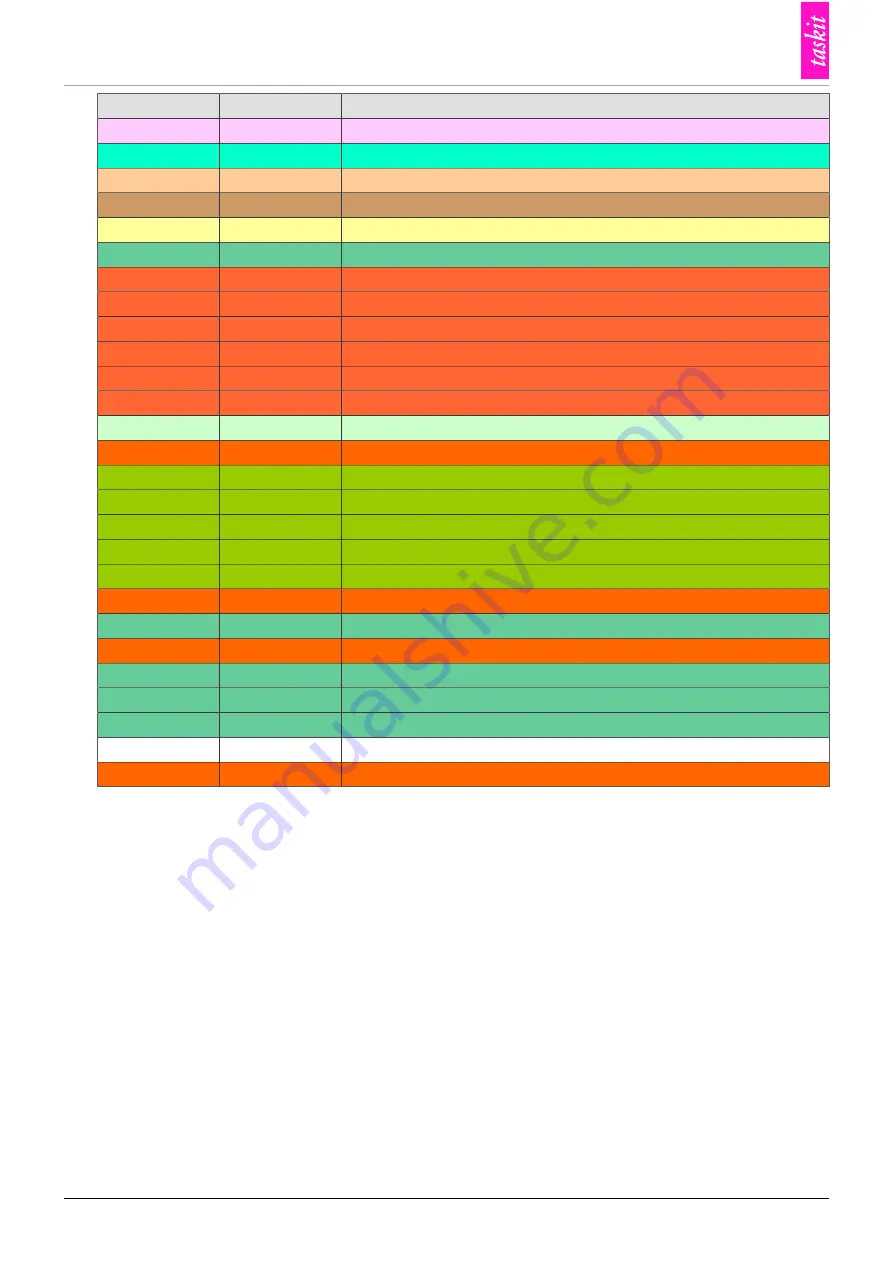

Address Map (Physical Address Space)

28

Address (Hex) Mnemonic

Function

FFFB 4000

ISI

Image Sensor Interface

FFFB 8000

PWM

Pulse Width Modulator

FFFB C000

EMAC

Ethernet Controller

FFFC C000

TRNG

True Random Number Generator

FFFD 0000

MCI_1

Multimedia Card / SD-Card Interface #1

FFFD 4000

TC3, TC4, TC5

3 Timer Counter, 16-Bit

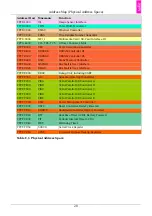

FFFF E200

ECC

Error Correction Controller

FFFF E400

DDRSDR

DDRAM Controller #1

FFFF E600

DDRSDR

DDRAM Controller #0

FFFF E800

SMC

Static Memory Controller

FFFF EA00

MATRIX

Bus Matrix User Interface

FFFF EC00

DMAC

Bus Matrix User Interface

FFFF EE00

DBGU

Debug Unit, including UART

FFFF F000

AIC

Advanced Interrupt Controller

FFFF F200

PIOA

32 Bit Parallel I/O Controller A

FFFF F400

PIOB

32 Bit Parallel I/O Controller B

FFFF F600

PIOC

32 Bit Parallel I/O Controller C

FFFF F800

PIOD

32 Bit Parallel I/O Controller D

FFFF FA00

PIOE

32 Bit Parallel I/O Controller E

FFFF FC00

PMC

Power Management Controller

FFFF FD00

RSTC

Reset Controller, Battery Powered

FFFF FD10

SHDWC

Shutdown Controller, Battery Powered

FFFF FD20

RTT

Real-time Timer 32 Bit, Battery Powered

FFFF FD30

PIT

Periodic Interval Timer 32 Bit

FFFF FD40

WDT

Watchdog Timer

FFFF FD50

SCKCR

Serial Clock Register

FFFF FD60

GPBR

4 General Purpose Backup Registers

Table C.1. Physical Address Space