Hardware Description

10

From the main clock oscillator, the CPU generates two further clocks by using two PLLs.

PLLA provides the processor clock (PCK) and the master clock (MCK). PLLB typically

provides the 48 MHz USB clock and is normally used only for this purpose. The clocks of

most peripherals are derived from MCK. These include EBI, USART, SPI, TWI, SSC, PIT

and TC.

Some peripherals like the programmable clocks and the timer counters (TC) can also run

on SLCK. The real time timer (RTT) always runs on SLCK.

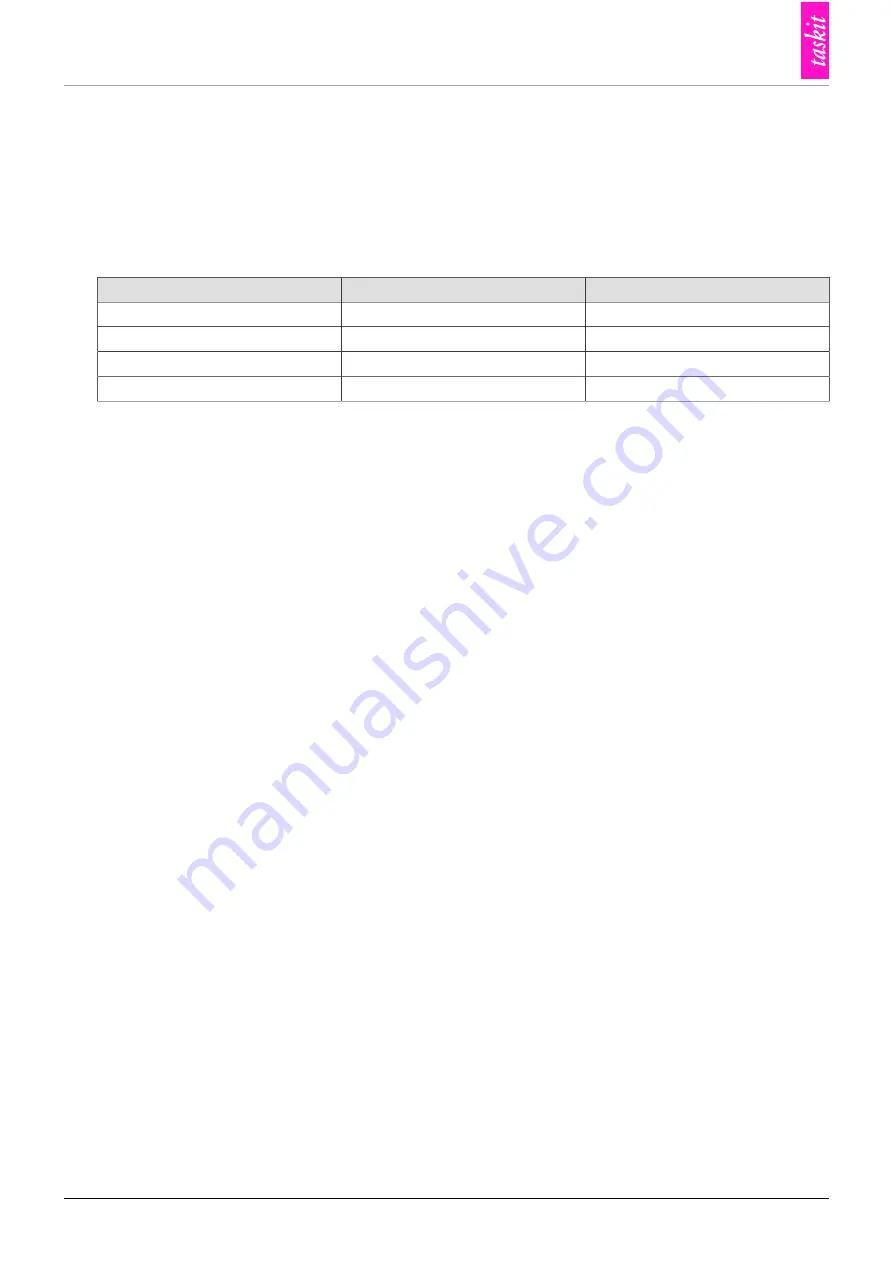

Clock

Frequency

Source

PCK (Processor Clock)

800 MHz

PLLA

MCK (Master Clock)

133 MHz

PCK/3

USB Clock

480 MHz

UPLL

Slow Clock

32.768 KHz

Slow Clock Oscillator

Table 4.3. AT91SAM9G45 Clocks

4.10.2. Programmable Clocks

The programmable clocks can be individually programmed to derive their input from

SLCK, PLLA, PLLB and Main Clock. Each PCK has a divider of 2, 4, 8, 16, 32 or 64.

The Stamp9G45 features two programmable clocks PCK0, PCK1.

4.11. Power Management Controller (PMC)

4.11.1. Function

The PMC has a Peripheral Clock register which allows to individually enable or disable the

clocks of all integrated peripherals by using their "Peripheral Identifier" (see Table B.1,

“Peripheral Identifiers”). The System Clock register allows to enable or disable each of

the following clocks individually:

• Processor Clock

• ISI Clock

• USB Host Clock (common for both channels)

• USB Device Clock

• Programmable Clocks

The PMC status register provides "Clock Ready" or, respectively, "PLL Lock" status bits

for each of these clocks. An interrupt is generated when any of these bits changes from

0 to 1. The PMC provides status flags for the

• Main Oscillator

• Master Clock

• PLLA