HGL Manual

5.0 PQconnect Connectivity

32

Read Parameters:

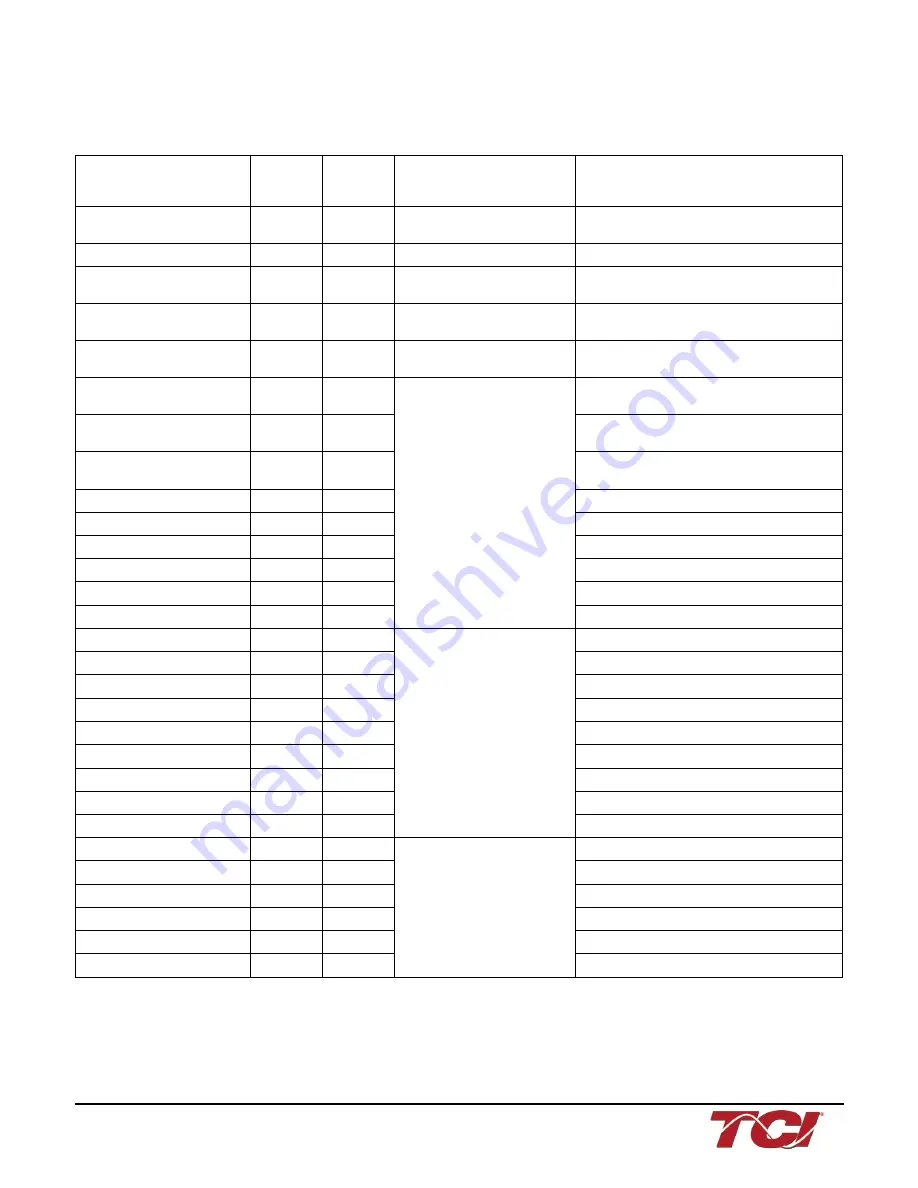

Table 21: Network Interface OUTPUT/Feedback Register Map

Parameter Name

I/O Reg

Address

Offset

Direction

Data Values and Examples

Description

DSP_SW_VER

12

Output

Two 8bit ASCII Characters

0x0141 = ASCII for "A1"

Software revision code for processor.

DSP_MODEL_NUM_RO

13

Output

102 = HGL

System Model Number

LINE_VOLTAGE

20

Output

4800 = 480 Vrms

Range: 120 to 690 Vrms

Filter input voltage

LINE_FREQ

21

Output

60 = 60 Hz

50 = 50 Hz

Filter input frequency

LINE_ROT

22

Output

1 = ABC Rotation Expected

2 = ACB Rotation Expected

Filter input phase orientation

V_LINE_AB_RMS

30

Output

Volts RMS

4800 = 480 Vrms

Range: 0 to 1000 Vrms

Source Utility Line Phase to Phase Voltage (A-

B)

V_LINE_BC_RMS

31

Output

Source Utility Line Phase to Phase Voltage (B-

C)

V_LINE_CA_RMS

32

Output

Source Utility Line Phase to Phase Voltage (C-

A)

V_LOAD_AB_RMS

50

Output

Filter Output Phase to Phase Voltage (A-B)

V_LOAD_BC_RMS

51

Output

Filter Output Phase to Phase Voltage (B-C)

V_LOAD_CA_RMS

52

Output

Filter Output Phase to Phase Voltage (C-A)

V_TRAP_A_RMS

70

Output

Filter Tuned Circuit Phase A Voltage

V_TRAP_B_RMS

71

Output

Filter Tuned Circuit Phase B Voltage

V_TRAP_C_RMS

72

Output

Filter Tuned Circuit Phase C Voltage

I_LINE_A_RMS

36

Output

Amps RMS

1,000 = 1,000 ARMS

Range: 0 to 1000 Arms

Filter Input Current Phase A

I_LINE_B_RMS

37

Output

Filter Input Current Phase B

I_LINE_C_RMS

38

Output

Filter Input Current Phase C

I_LOAD_A_RMS

56

Output

Filter Output Current Phase A

I_LOAD_B_RMS

57

Output

Filter Output Current Phase B

I_LOAD_C_RMS

58

Output

Filter Output Current Phase C

I_TUNE_A_RMS

76

Output

Filter Tuned Circuit Current Phase A

I_TUNE_B_RMS

77

Output

Filter Tuned Circuit Current Phase B

I_TUNE_C_RMS

78

Output

Filter Tuned Circuit Current Phase C

I_LINE_A_THD

39

Output

% THID

50 = 5.0% THID

Phase A THID for line current feedback

I_LINE_B_THD

40

Output

Phase B THID for line current feedback

I_LINE_C_THD

41

Output

Phase C THID for line current feedback

I_LOAD_A_THD

59

Output

Phase A THID for load current feedback

I_LOAD_B_THD

60

Output

Phase B THID for load current feedback

I_LOAD_C_THD

61

Output

Phase C THID for load current feedback