3-36

System 3

RX7 Stimulator Base Station

RX

Architecture

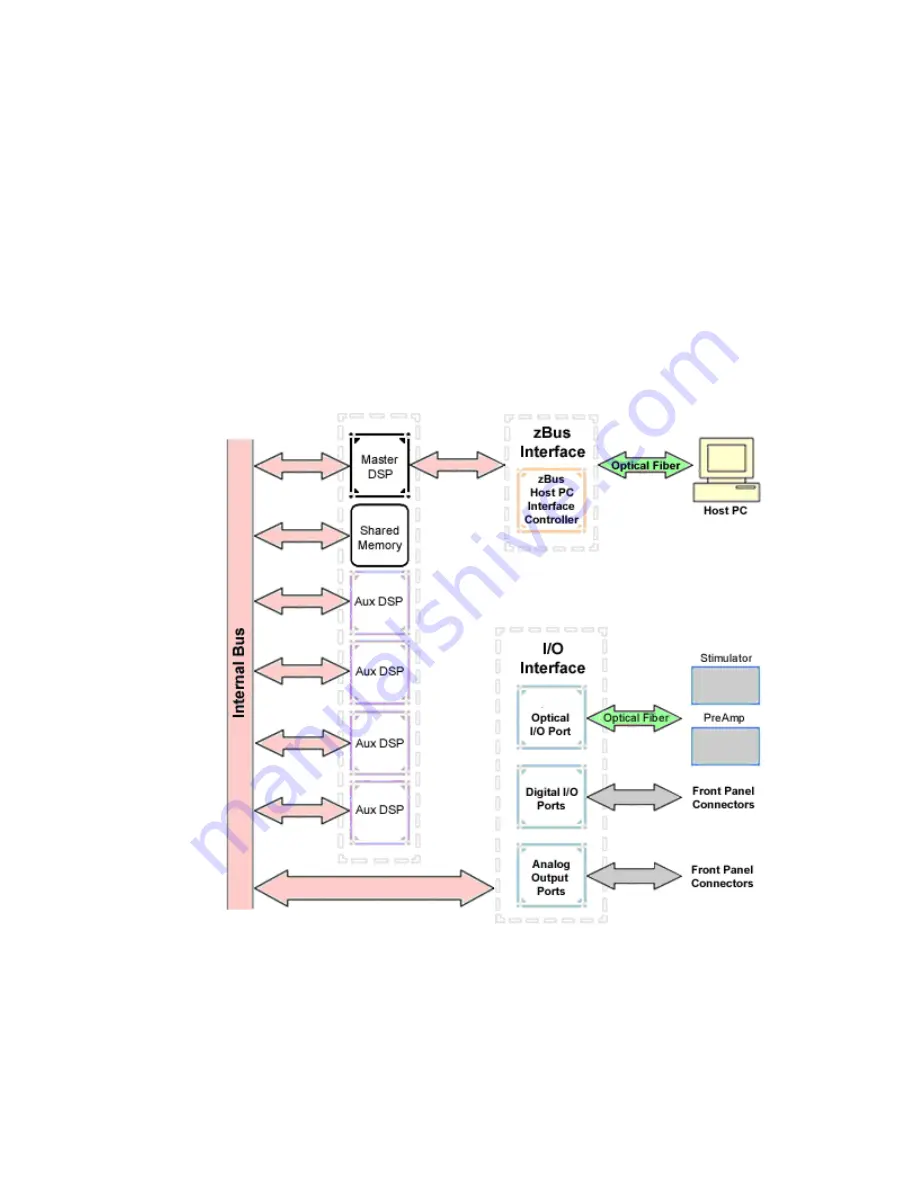

Each RX multiprocessor device is equipped with either two or five digital signal

processors (DSPs). The multi-DSP architecture allows processing tasks to be

distributed across multiple processors and enables data to be transferred to the PC

quickly and efficiently. The DSPs include one master and one or four auxiliary

DSP(s). 128 MB SDRAM of system memory is shared by all DSPs. When

designing circuits the maximum number of components for each RX DSP is 256.

Each DSP communicates with an internal bus to send and receive information from

the I/O controller and the shared memory. The master DSP supervises overall

system boot up and operation. The master DSP also acts as the main data interface

between the zBus (host PC) and the multi-DSP environment.

Because the zBus communicates only with the master processor, these devices

operate most efficiently when the circuit related processing tasks assigned to the

master DSP are minimized, allowing more processor power (cycles) for

communication and overhead tasks.

The RX7 contains two DB25 connectors for interfacing with 40 bits of digital I/O

and 4 channels of analog output. A BNC connector is provided for access to the

first analog output channel. One or two fiber optic Medusa preamp ports enable

connections for up to 32 channels of analog input.