Installing & Working With System Components 4-4

4.03 SYSTEM CONTROLLER OVERVIEW

The PicoPower (Cirrus Logic subsidiary) PT86C768/PT86C718 System Controller used

on the VIPer808 board is a two-chip solution packaged in 176-pin VQFP’s. This chipset

contains power management features making it ideal for designing energy efficient

computer systems and high performance applications.

The System Controller was designed to support 32-bit 486 CPUs, capitalizing on the

unique features found in the SL-Enhanced series. It incorporates PicoPower’s Power On

Demand

technology, providing unsurpassed power management features (explained in

section 8).

The System Controller also includes features like a high performance DRAM Controller,

Clock and Reset Interface, a Local Bus IDE Drive Interface for high performance disk

subsystem, and integrated 82C206 functions.

The System Controller is 100% IBM PC/AT compatible. It includes three 8254

Counter/Timers, two 8237 DMA Controllers and two 8259 Interrupt Controllers.

4.03.1 DMA CONTROLLERS

The VIPer808 supports seven Direct Memory Access (DMA) channels. The parallel port's

ECP mode can be configured to use Channel 1 or 3. Channel 2 is reserved for the Floppy

controller. Channel 4 is used to cascade Channels 0 through 7 to the microprocessor.

Channel 5 is available for the Ethernet port. Note that with Plug and Play, DMA channels

for I/O devices and the Ethernet can be modified via software per system requirements.

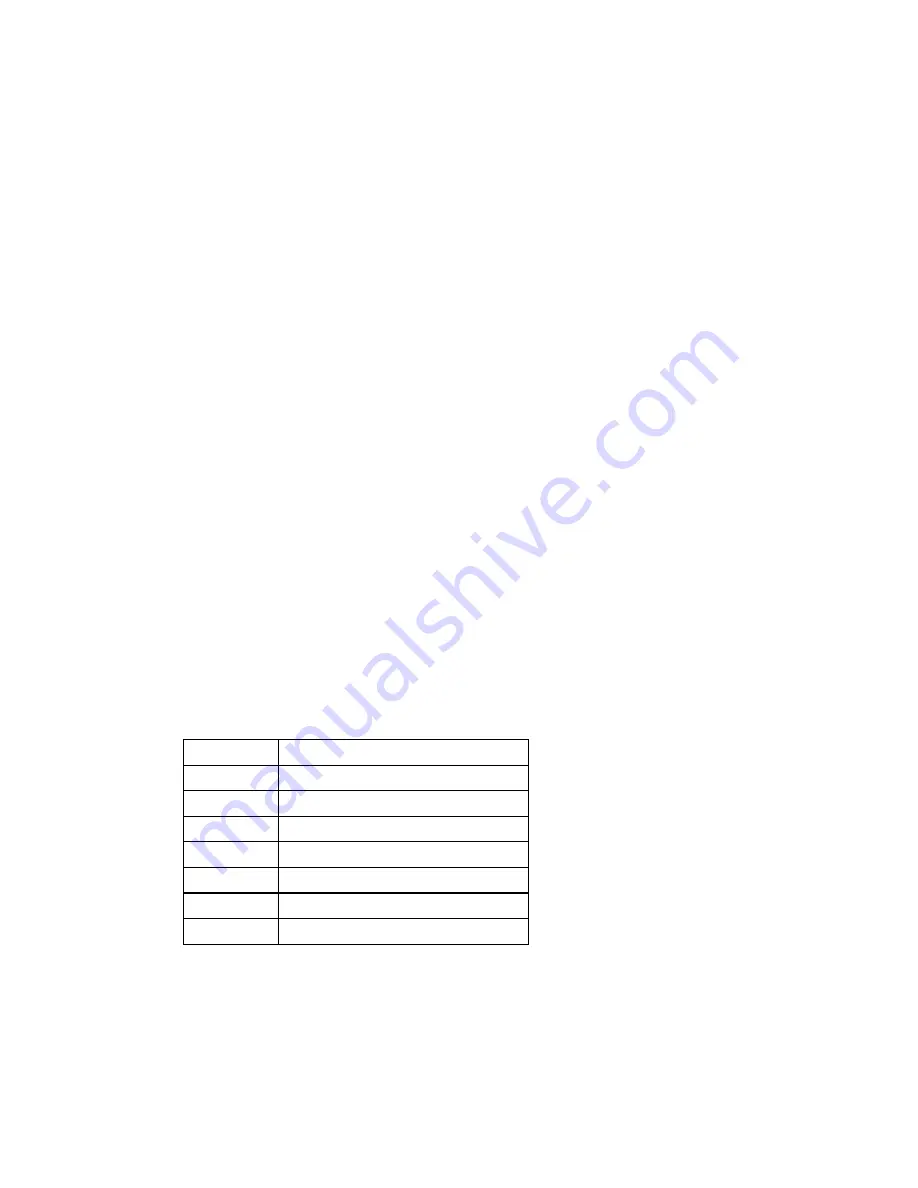

TABLE 4-1:

8237 DMA Controllers

DMA 0

Available

DMA 1

Available (ECP)

DMA 2

Floppy controller

DMA 3

Available (ECP)

DMA 4

Cascade controller # 1

DMA 5

Available (Ethernet)

DMA 6

Available

DMA 7

Available

Summary of Contents for VIPer808

Page 21: ...Installing Memory 2 3 DIAGRAM 2 1 Assembly Top...

Page 22: ...Installing Memory 2 5 DIAGRAM 2 2 Assembly Bottom...

Page 26: ...Setting Jumpers 3 3 DIAGRAM 3 1 VIPer808 Jumper Locations with Default Settings...

Page 28: ...Setting Jumpers 3 6 TABLE 3 1a Jumper Settings W1 W4 W13 W14...

Page 29: ...Setting Jumpers 3 7 TABLE 3 1b AMD DX2 DX4 CPU Jumper Settings W1 W15 W15C...

Page 30: ...Setting Jumpers 3 8 TABLE 3 1c AMD 5x86 CPU Jumper Settings W1 W15 W15C...

Page 31: ...Setting Jumpers 3 9 TABLE 3 1d Intel CPU Jumper Settings W1 W15 W15C...

Page 32: ...Setting Jumpers 3 10 TABLE 3 1e SGS CPU Jumper Settings W1 W15 W15C...

Page 33: ...Setting Jumpers 3 11 TABLE 3 1f Jumper Settings W18 W20 W23...

Page 92: ...Memory I O Maps B 1 APPENDIX B MEMORY I O MAPS B 01 MEMORY MAPS DIAGRAM B 1 Memory Map Diagram...

Page 96: ...Mechanical Layout Block Diagram C 3 DIAGRAM C 1 Mechanical Specifications...