General

Information—7A42

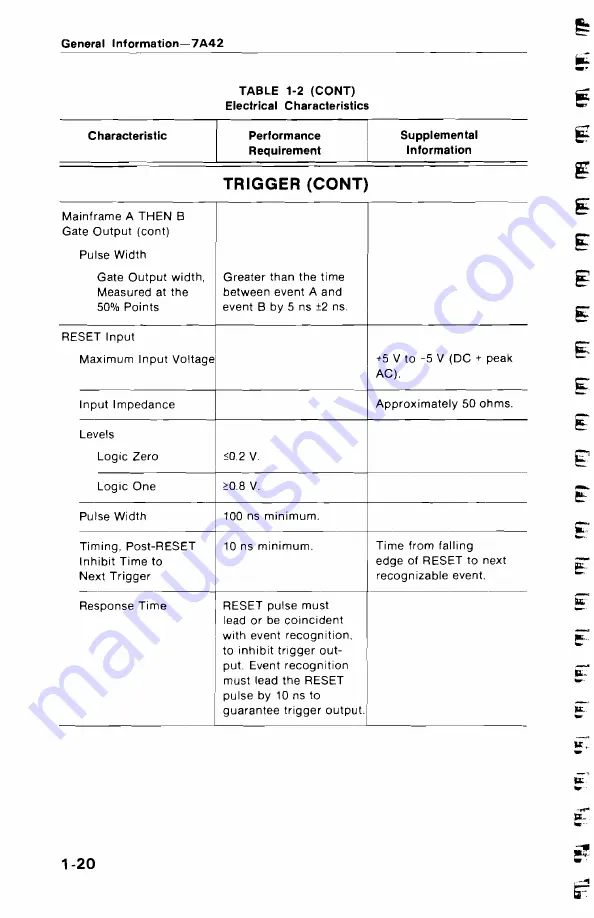

TABLE

1-2 (CONT)

Electrical

Characteristics

Characteristic

Performance

Supplemental

Requirement

Information

TRIGGER

(CONT)

Mainframe

A

THEN

B

Gate

Output

(cont)

Pulse

Width

Gate

Output

width,

Measured

at

the

50%

Points

Greater

than

the

time

between

event

A

and

event

B

by

5

ns

±2

ns.

RESET

Input

Maximum

Input

Voltage

+5 V

to

-5 V

(DC

+

peak

AC).

Input

Impedance

Approximately

50

ohms.

Levels

Logic

Zero

<0.2

V.

Logic

One

>0.8

V.

Pulse

Width

100 ns

minimum.

Timing,

Post-RESET

Inhibit

Time

to

Next

Trigger

10

ns

minimum.

Time

from

falling

edge of

RESET

to

next

recognizable

event.

Response

Time

RESET

pulse

must

lead

or

be

coincident

with

event

recognition,

to

inhibit

trigger out

put.

Event

recognition

must lead

the

RESET

pulse

by

10

ns

to

guarantee

trigger

output.

1-20