S42

Hardware User Guide

1VV0301303 Rev. 11

Page 35 of 85

2021-05-06

Not Subject to NDA

4.2.

General Pin Description

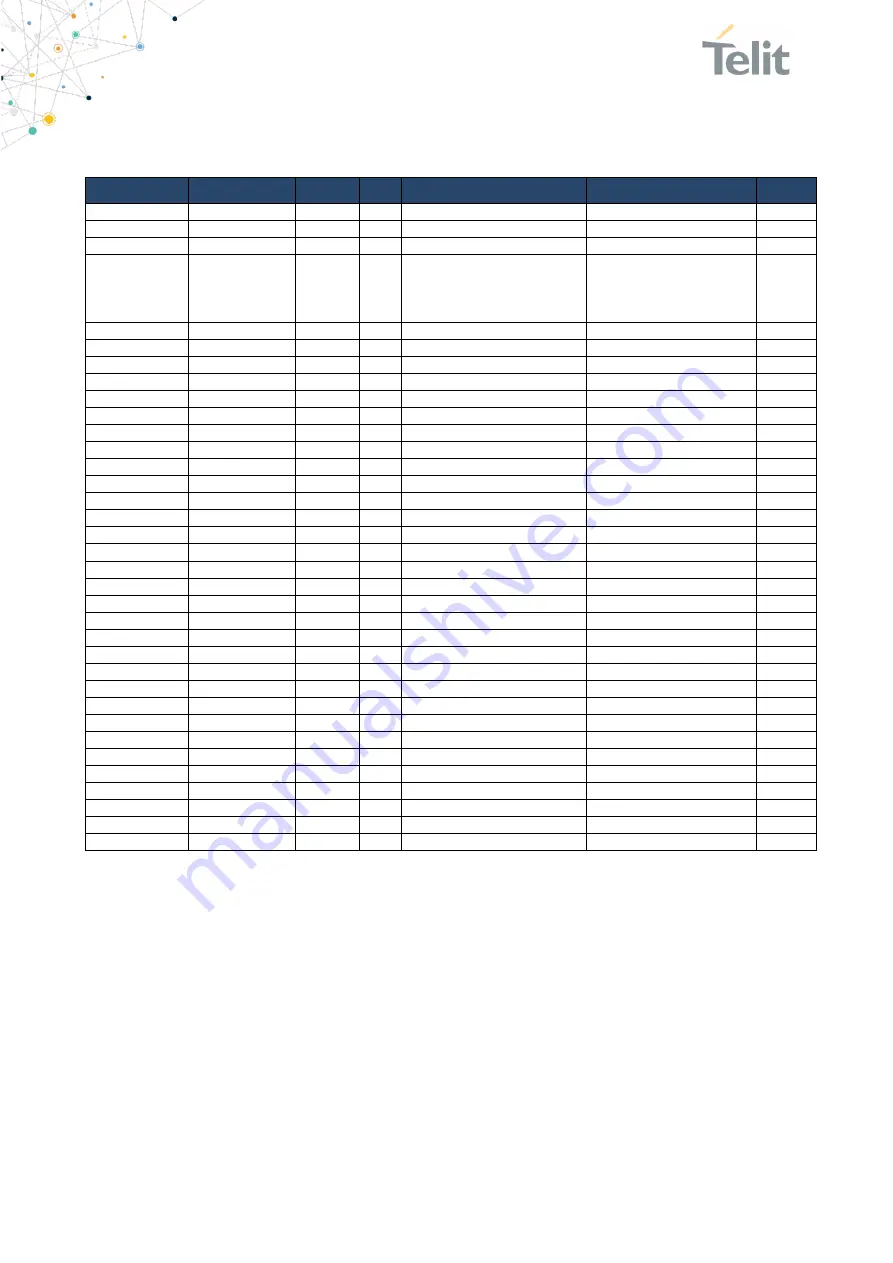

Type: PU = pull-up; PD = pull-down; PWR = Power; I = Input; O = Output; I/O = bidir.; OD = open drain; PP = push/pull;

RF: Radio; I-DIS

–

Input Buffer Disconnected

Pin Name

Signal

Type

Act

Function

Alternate Function

Notes

E-6

VSUP1

PWR

+3,0V nom.

F-6

VSUP2

PWR

+3,0V nom

C-1

not connected

none

May be connected to VSUP

A-7, E-7, F-7,

B-[5,6,7,8],

C-[5,6,7,8],

D-8, E-8, F-8

GND

PWR

Ground

All GND pins must be

connected

A-8

ANT PIN

none

reserved for ext. antenna

(4,9)

B-1

EXT-RES#

I-PU

L

User Reset

A-6

XL-IN

I/O

XTAL 32,768kHz

F-4

UART-TXD

O-PP

Serial Data OUT

(6)

D-2

UART-RXD

I

Serial Data IN

(6)

D-7

UART-RTS#

O-PU (1) L

Flow Control/IUC

(1,6)

F-3

UART-CTS#

I-PD

L

Flow Control/IUC

(6,8)

B-4

IUR-OUT#

O-PP

L

UICP Control

(AIN2)

(8)

D-5

IUR-IN#

I-DIS

L

UICP Control

(AIN5)

(8)

D-3

GPIO[0]

I/O

GPIO

I2C-SCL

(3,5)

B-2

GPIO[1]

I/O

GPIO

I2C-SDA, AIN7

(3,5)

D-1

GPIO[2]

I/O

GPIO

SPI-MOSI

(3,5)

E-4

GPIO[3]

I/O

GPIO

AIN0

(3,5)

D-4

GPIO[4]

I/O

GPIO

AIN6

(3,5)

F-2

GPIO[5]

I/O

GPIO

SPI-MISO, AIN3

(3,5)

C-4

GPIO[6]

I/O

GPIO

AIN1

(3,5)

C-3

GPIO[7]

I/O

GPIO

AIN4

(3,5)

E-2

GPIO[8]

I/O

GPIO

SPI-SCK

(3,5)

A-3

NFCANT1

RF

NFC-Antenna

A-1

GPIO[10]

I/O

GPIO

(3,5)

A-4

NFCANT2

RF

NFC-Antenna

A-2

GPIO[9]

I/O

GPIO

(3,5)

F-1

TESTMODE#

I-PU (7) L

Testmode Enable

(6)

E-1

BOOT0

I-PD (7)

reserved

(6)

E-3

SWDIO

I/O-PU

Serial Wire Debug (data)

D-6

SWCLK

I-PD

Serial Wire Debug (clock)

C-2

GPIO[13]

I/O

GPIO

(3,5)

B-3

GPIO[11]

I/O

GPIO

(3,5)

A-5

XL-OUT

I/O

XTAL 32,768kHz

F-5

GPIO[14]

I/O

GPIO

(3,5)

E-5

GPIO[12]

I/O

GPIO

(3,5)

Notes:

(1) a discrete pull up resistor 470k is used

(3) function depends on firmware

(4) DNU: Do Not Use, Do Not Connect

(5) GPIO pin. These pins may be programmed as analog-in, i-disconnected, i-float, i-pu, i-pd, o-pp (output push/pull),

o-od (output open drain), o-os (output open source) or some alternate function; refer to

(6) signal must be accessible for homologation purposes. Refer to 3.10 Test Mode

(7) signals sampled at startup time. TESTMODE# is I-PU, BOOT0 is I-PD during sampling time only, I-DIS otherwise

(8) Pin Type depends on UICP status. Refer to 3.3.5 Dynamic I/O Signal Type Changes Depending on UICP Status

(9) for compatibility to SR this pin is reserved for an external antenna and must be left open

Table 10: General Pin Assignment