S42

Hardware User Guide

1VV0301303 Rev. 11

Page 40 of 85

2021-05-06

Not Subject to NDA

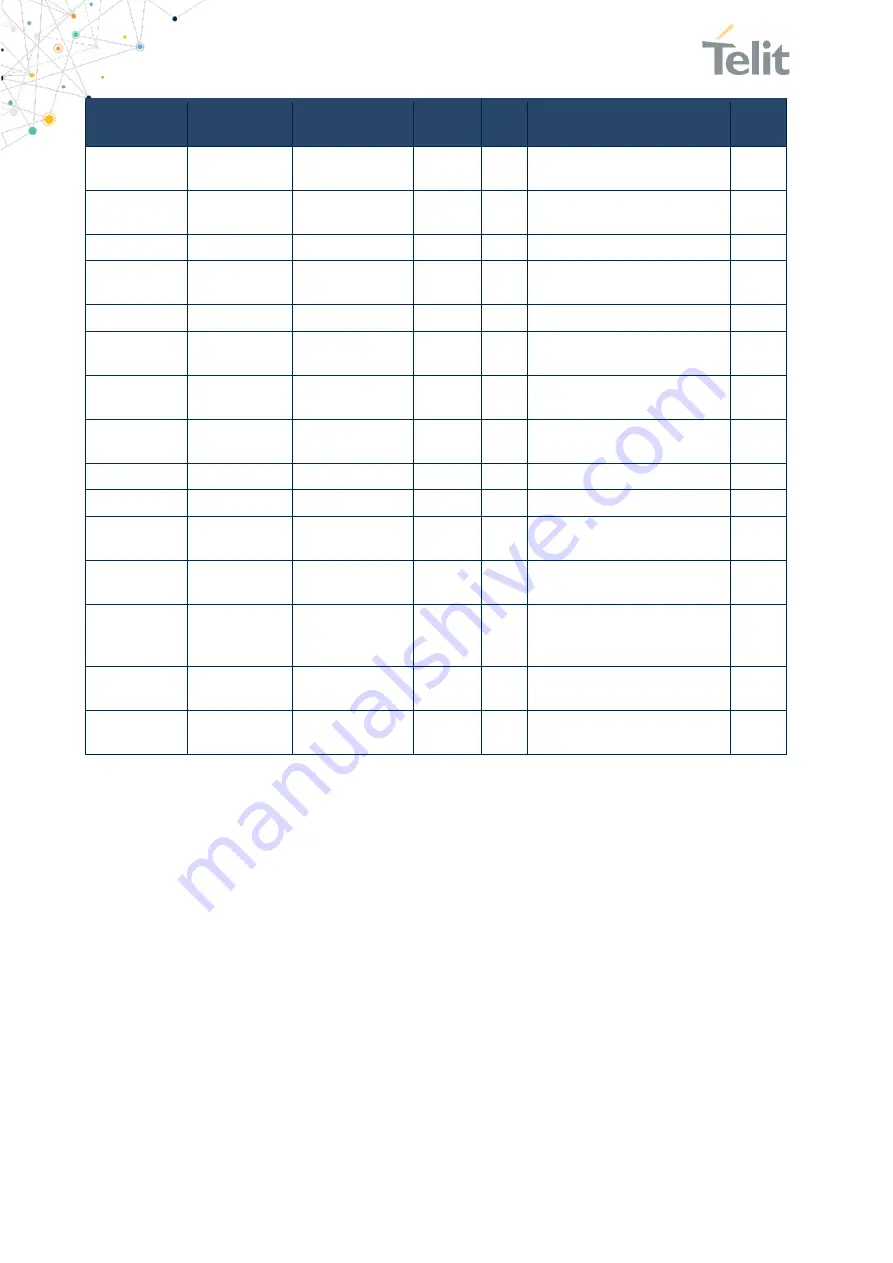

Pin Name

Signal

ADC/LUA

Function

Type

Act

Description

Note

C-3

GPIO[7]

AIN4

DIO3

I/O

DIS

Analog Input 4

Digital In/Output 3

(3)

E-2

GPIO[8]

SPI-SCK

O-PP

DIS

SPI Clock

(3)

A-3

NFCANT1

NFC

RF

A-1

GPIO[10]

SPI_CS

O-PP

DIS

L

SPI Chip select

(3)

A-4

NFCANT2

NFC

RF

A-2

GPIO[9]

DIO4

I/O

DIS

Digital In-/Output 4

(3)

F-1

TESTMODE#

reserved

I-PU

DIS

L

connect to test pad

(6,7)

E-1

BOOT0

reserved

I-PD

DIS

connect to test pad

(6,7)

E-3

SWDIO

reserved

I/O-PU

leave open (Serial Wire Debug) (4)

D-6

SWCLK

reserved

I-PD

leave open (Serial Wire Debug) (4)

C-2

GPIO[13]

DIO7

I/O

DIS

Digital In-/Output 7

(3)

B-3

GPIO[11]

DIO5

I/O

DIS

Digital In-/Output 5

(3)

A-5

XL-OUT

XTAL

LFXO

32,768kHz Slow Clock crystal

(optional, leave open without

crystal)

F-5

GPIO[14]

DIO8

I/O

DIS

Digital In-/Output 8

(3)

E-5

GPIO[12]

DIO6

I/O

DIS

Digital In-/Output 6

(3)

Notes:

(1) a discrete pull up resistor is used

(3) function depends on firmware

(4) DNU: Do not use, do not connect

(6) signal must be accessible for homologation purposes. Refer to

(7) signals sampled at startup time. TESTMODE# is I-PU, BOOT0 is I-PD during sampling time only, I-DIS otherwise

(8) Pin type depends on UICP status. Refer to

(9) for compatibility to SR this pin is reserved for an external antenna and must be left open

Table 13: Application specific pin assignments, ADC/LUA