S42

Hardware User Guide

1VV0301303 Rev. 11

Page 29 of 85

2021-05-06

Not Subject to NDA

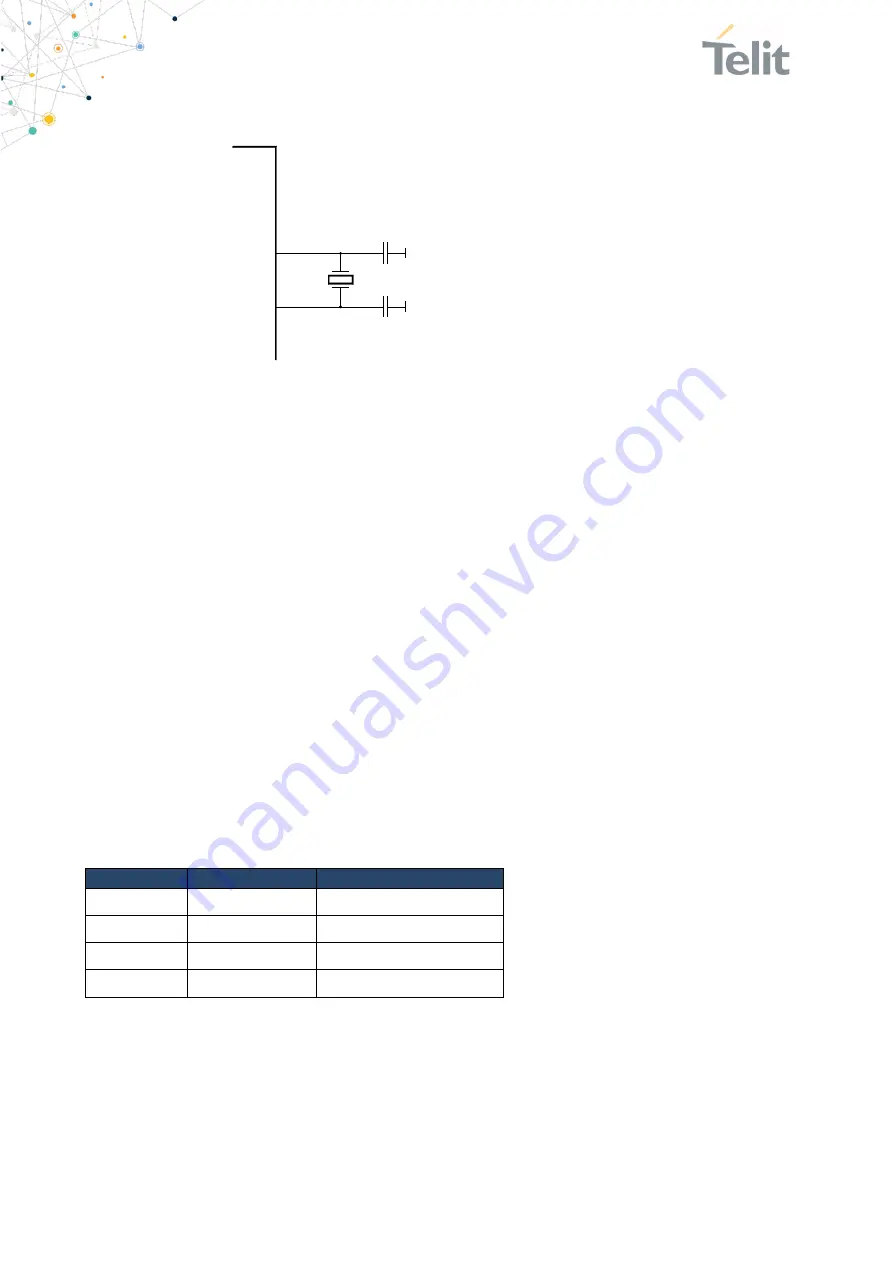

C

L

=

(C1+C

pin

+C

s

) * (C2+C

pin

+C

s

) / (C1+C2+2*C

pin

+2*Cs), or

C1, C2 = (2*C

L

–

C

pin

–

C

s

)

C

pin

: see Table

C

s

: stray

capacitance, depends on layout

Figure 15: S42 connection of external XTAL

3.10.

Test Mode

For homologation purposes, the ability of test mode opera

tion like “S42

Testmode” or “Direct two wire UART Testmode” (DTM) is mandatory. The Direct Test

Mode (as defined by the Bluetooth SIG) and S42 Testmode are part of the

S42 firmware. Please refer to

. For EMC measurements the use of

the S42 Testmode is recommended.

For enabling the different test modes, the S42 provides two IO pins.

•

The pin Testmode is low active. Active in the following table means connect to

GND.

•

The pin Boot0 is high active. Active in the following table means connect to VDD.

•

The other two combinations start the bootloader for firmware update of the

programmed firmware. These two modes are not scope of this document.

The following table shows the possible combinations:

Testmode#

Boot0

Mode

Active

Inactive

Testmode (38400, 8N1)

Active

Active

DTM (19200, 8N1)

Inactive

Active

Bootloader (15200, 8N1)

Inactive

Inactive

Firmware

Table 7: Testmode# / Boot0 Logic

To enter and use S42 Testmode or DTM, access to the following signals is

required:

•

BOOT0

XL-IN

S42

A-6

Slow Clock

XL-OUT

A-5

32,768kHz

CL: 9pF

C1

C2

C1, C2 ~ 12pF