S50 Hardware User Guide

1VV0301505 Rev. 3

Page 18 of 60

2021-05-05

Not Subject to NDA

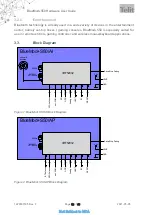

4.3.3.

Serial Interface with UICP

A substantially saving of power during idle phases can be achieved (see when the UICP

protocol is used (refer to [2]). This protocol should be implemented on the host side as

well. Signals IUR-IN# and IUR-OUT# should be connected to the host and may be mapped

to DSR and DTR, if an RS232-style (DTE-type) interface is used (see Figure 7).

UART-TXD

GND

UART-RXD

CTS#

UART-RXD

UART-TXD

B

lu

eM

o

d

+

Sx

H

o

st

RTS#

CTS#

RTS#

IUR_OUT#

IUR_IN#

IUR_OUT# / DTS

IUR_IN# / DTR

Figure 7: S50 Serial Interface Supporting UICP

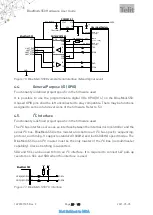

If I/O line availability at the host side is extremely tight, 2 I/O lines could be saved by using

the following scheme. This would come at the cost of:

•

The host is not allowed to enter sleep mode.

•

The host must accept incoming data at all times and is not able to stop the

Sx sending data. This may be difficult to control for all scenarios and

adds the risk that data gets lost.

•

The host does not implement UICP, but wake-up BT via GPIO.

UART-TXD

GND

UART-RXD

IUC_IN# / CTS#

UART-RXD

UART-TXD

B

lu

eM

o

d

+

Sx

H

o

st

RTS#

CTS#

IUC_OUT# / RTS#

IUR_OUT#

IUR_IN#

BM+Sx-WKUP

Figure 8: Five Wire Interface Supporting UICP