Application Note P4097

© TeraTron GmbH

Page 10 of 21

V1.1, 07.06.01

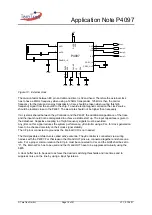

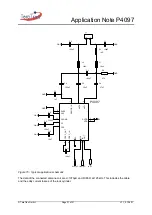

150nF

CF

10nF

DEMOD_IN

VSS

from Ant.

CAGND

GND

100nF

1.5nF

DVSS

CDC

Figure 5.: Ground signal layout

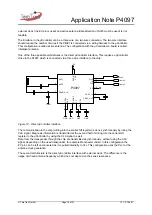

The buffer capacitors should be located close between the DV

DD

and DV

SS

pins. Any voltage drop due

to copper resistance or track inductance will be seen via the antenna on the DEMOD_IN pin and will

be demodulated. This should be regarded for the larger electrolytic capacitor as well as for the

ceramic capacitor. Using two sets of capacitors makes it easier to place and route them on the circuit

board. One set is buffering the high current supply DV

DD

and DV

SS

, whereas the other capacitors (or

just the ceramic one) buffers the analog supply V

DD

and V

SS

.

The signal DEMOD_IN is very susceptible against capacitive coupling of noisy tracks. The capacitive

voltage divider should be located close to the input pin and connected to a proper analog ground. A

ripple voltage or a voltage drop relative to V

SS

is coupled into the DEMOD_IN pin due to the capacitor

ratio much stronger than the useful signal coming from the antenna.

The CDEC capacitor which connects the sampler with the filter is susceptible against capacitive

coupling of noise. The capacitor should be located close to the chip and the tracks should be short

and not close to other traces with fast changing voltage levels.

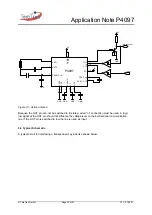

The antenna connection, if an external antenna is used, should be bypassed with two small ceramic

capacitors to ground close to the connector. This suppresses high frequency voltages to ground which

are picked up by the wiring harness and reduces the radiation out of the circuit into the wiring harness.

Other connector pins which are connected to a wiring harness should be treated similar. The ground

plane to which these capacitors are connected should be routed carefully to achieve a low impedance

for high frequencies.

Unused pins except the CF pin in external clock mode can be left open as the inputs are internally

pulled to ground and outputs are push-pull types without tri-state mode and therfore defined voltage

levels.

3.8 EMI Filter

In applications where the functionality even under the influence of strong electromagnetic fields is

required, additional filter circuitry for connecting the antenna coil with the P4097 is recommended. The

filter shown below suppresses high frequent voltages which could be picked up by the antenna cable

or the antenna itself. Because of the –60dB level of the useful transponder signal in relation to the

125kHz carrier frequency the communication is by nature susceptible against electromagnetic

interference.