Application Note P4097

© TeraTron GmbH

Page 8 of 21

V1.1, 07.06.01

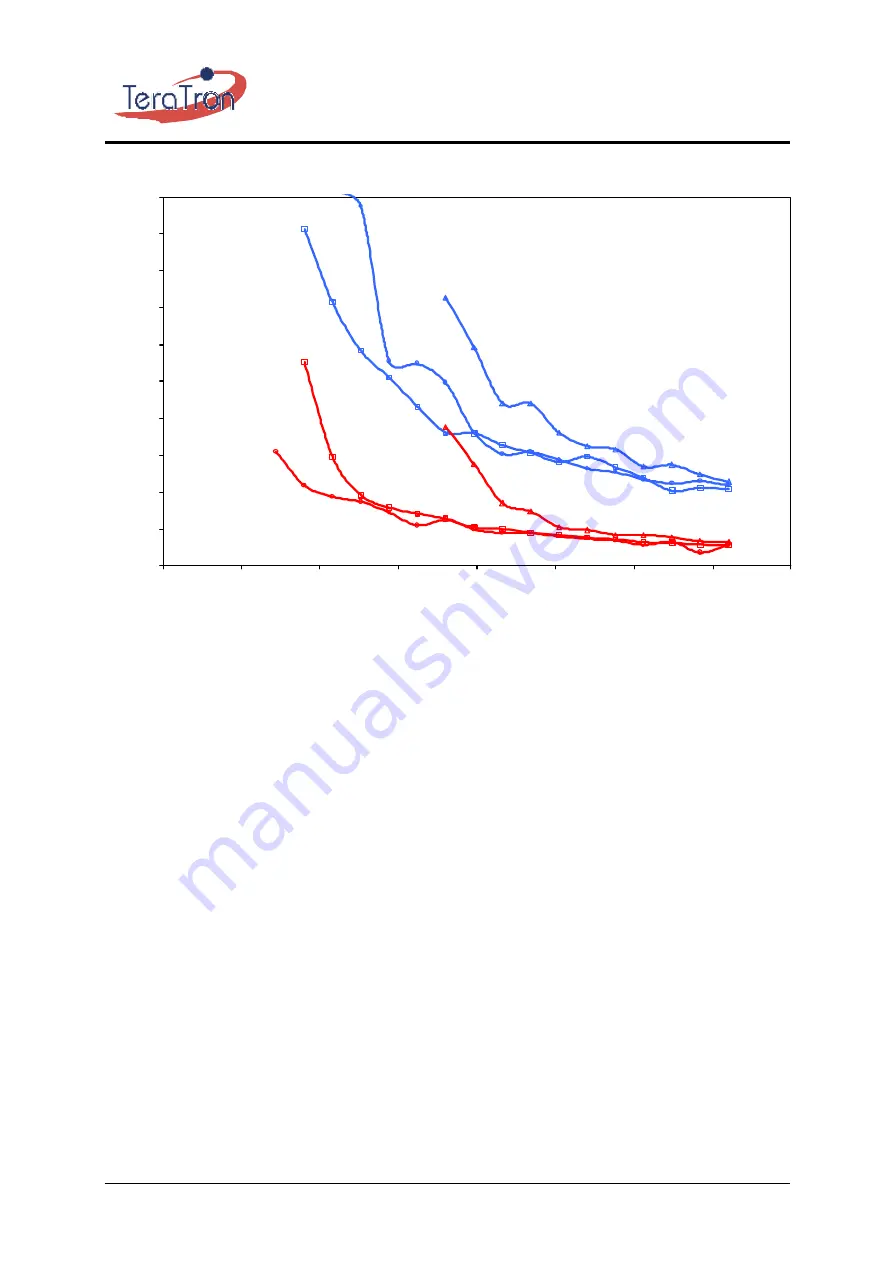

Red trace:

Amplitude demodulation

Circle:

Gain 960

Blue trace:

Phase demodulation

Square:

Gain 480

Triangle:

Gain 240

Figure 4.: Jitter as function of modulation depth

The diagram shows that the sensitivity is typically about 0.5mV, 1mV and 2mV for a gain of 960, 480

and 240. If the jitter is regarded a gain of 480 achieves the best result for both, the phase and the

amplitude demodulation.

3.4 Phase Lock Loop

With the help of the PLL the antenna is driven with it’s series resonance frequency. The input signal

for this PLL is the signal at the DEMOD_IN pin, the same signal which is demodulated.

Therefore the phase of this signal relative to the antenna driver signal is important as the PLL will not

lock correctly with shifted signals. This is the reason for choosing a capacitive voltage divider for the

DEMOD_IN pin as the phase shift is not affected by parasitic capacitance caused by the PCB tracks

or the pin to pin spacing.

For the same reason the polarity of the ANT1 and ANT2 antenna driver pins is important. The PLL

locks only if the ANT2 pin is connected to the DEMOD_IN pin via the series resonance capacitor, not

the via the coil. Swapping ANT2 and ANT1 or the capacitor and the inductor causes a 180° phase shift

and the PLL is not able to lock which means the antenna is driven on the wrong frequency.

The lock frequency of the PLL is preserved as analog voltage in the external capacitor during the

modulation of the antenna driver. When the antenna is switched on again this hold mode is switched

off after a few 50µs. The antenna voltage has reached a steady state then and the PLL can continue

working with the same voltage level as before the modulation. If the antenna is continuously

modulated with a frequency of more than 2.5kHz the chip is not able to leave this hold mode.

Therefore the frequency of the PLL will drift away as the capacitors are discharged by leakage

currents. This is a process with a time constant at room temperature of minutes.

0%

2%

4%

6%

8%

10%

12%

14%

16%

18%

20%

0,0

0,5

1,0

1,5

2,0

2,5

3,0

3,5

4,0

Modulation [mV]

Relative Standard Deviation of Pulse Width