DS_1209F_004

73S1209F Data Sheet

Rev. 1.2

81

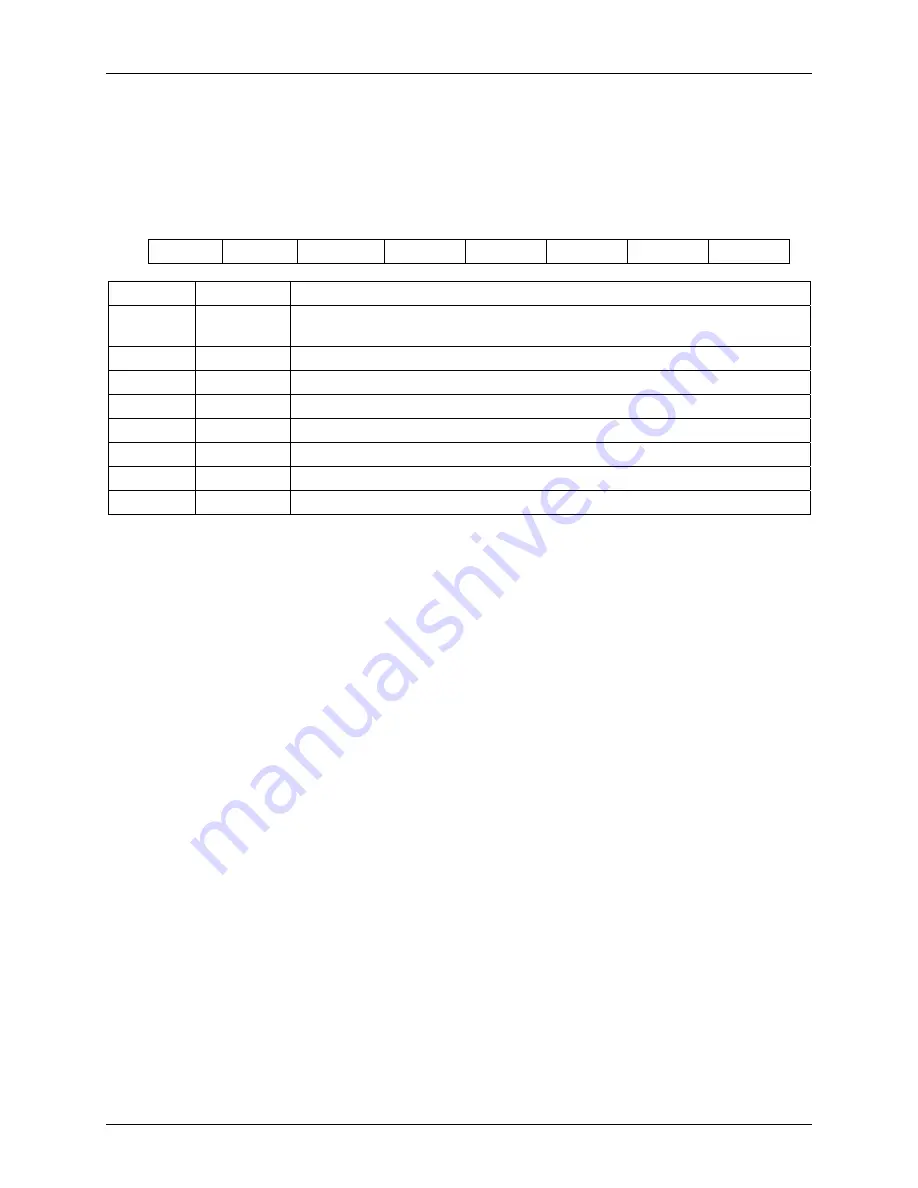

Smart Card Interrupt Enable Register (SCIE): 0xFE02

Å

0x00

When set to a 1, the respective condition can cause a smart card interrupt. When set to a 0, the

respective condition cannot cause an interrupt. When disabled, the respective bit in the Smart Card

Interrupt register can still be set, but it will not interrupt the MPU.

Table 75: The SCIE Register

MSB

LSB

WTOIEN CDEVEN VTMREN RXDAEN TXEVEN TXSNTEN TXEREN RXEREN

Bit Symbol

Function

SCIE.7 WTOIEN

Wait Timeout Interrupt Enable – Enable for ATR or Wait Timeout Interrupt.

In sync mode, function is RLIEN (RLen = max.) interrupt enable.

SCIE.6

CDEVEN

Card Event Interrupt Enable.

SCIE.5

VTMREN VCC Timer Interrupt Enable.

SCIE.4

RXDAEN

Rx Data Available Interrupt Enable.

SCIE.3

TXEVEN

TX Event Interrupt Enable.

SCIE.2

TXSNTEN TX Sent Interrupt Enable.

SCIE.1

TXEREN

TX Error Interrupt Enable.

SCIE.0

RXEREN

RX Error Interrupt Enable.