73S1209F Data Sheet

DS_1209F_004

102

Rev.

1.2

1.7.14 VDD Fault Detect Function

The 73S1209F contains a circuit to detect a low-voltage condition on the supply voltage V

DD

. If enabled,

it will deactivate the active internal smart card interface when V

DD

falls below the V

DD

Fault threshold. The

register configures the V

DD

Fault threshold for the nominal default of 2.3V* or a user selectable threshold.

The user’s code may load a different value using the FOVRVDDF bit =1 after the power-up cycle has

completed

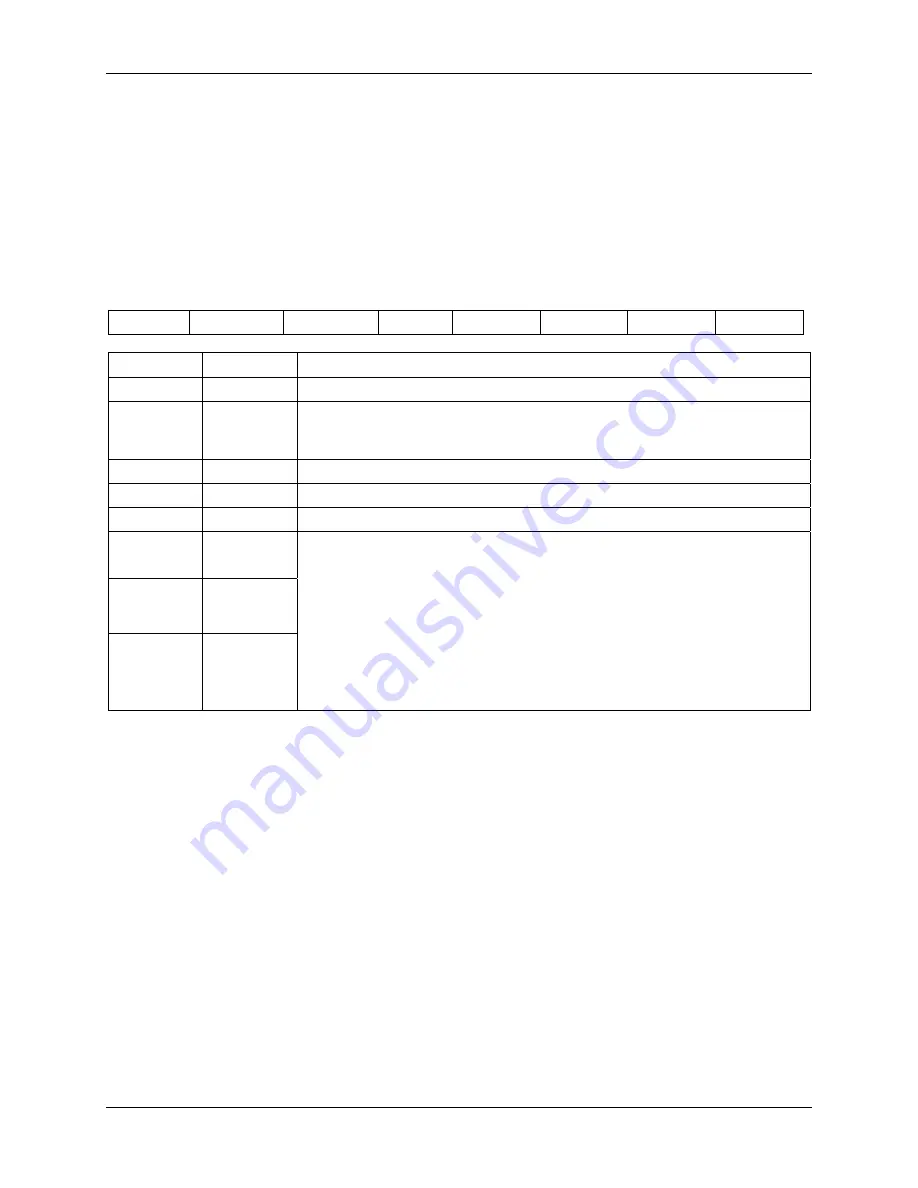

VDDFault Control Register (VDDFCtl): 0xFFD4

Å

0x00

Table 109: The VDDFCtl Register

MSB

LSB

– FOVRVDDF

VDDFLTEN

– STXDAT.3 VDDFTH.2 VDDFTH.1 VDDFTH.0

Bit Symbol

Function

VDDFCtl.7 –

VDDFCtl.6 FOVRVDDF

Setting this bit high will allow the VDDFLT(2:0) bits set in this register to

control the VDDFault threshold. When this bit is set low, the VDDFault

threshold will be set to the factory default setting of 2.3V*.

VDDFCtl.5 VDDFLTEN Set = 1 will disable VDD Fault operation.

VDDFCtl.4 –

VDDFCtl.3 –

VDDFCtl.2 VDDFTH.2

VDD Fault Threshold.

Bit value(2:0) VDDFault voltage

000

2.3 (nominal default)

001

2.4

010

2.5

011

2.6

100

2.7

101

2.8

110

2.9

111

3.0

VDDFCtl.1 VDDFTH.1

VDDFCtl.0 VDDFTH.0

* Note: The V

DD

Fault factory default can be set to any threshold as defined by bits VDDFTH(2:0). The

73S1209F has the capability to burn fuses at the factory to set the factory default to any of these

voltages. Contact Teridian for further details.