73S1209F Data Sheet

DS_1209F_004

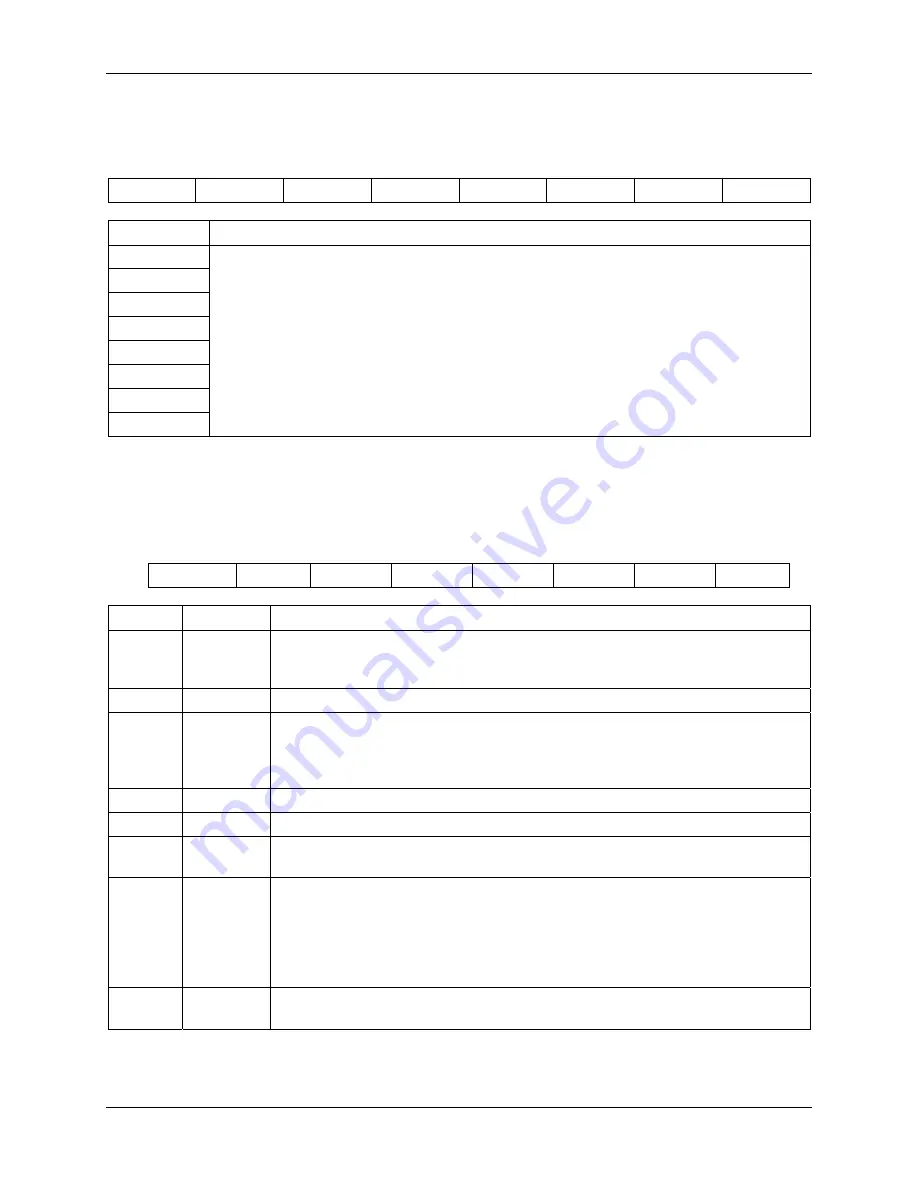

STX Data Register (STXData): 0xFE07

Å

0x00

Table 80: The STXData Register

MSB

LSB

STXDAT.7 STXDAT.6 STXDAT.5 STXDAT.4 STXDAT.3 STXDAT.2 STXDAT.1 STXDAT.0

Bit Function

STXData.7

Data to be transmitted to smart card. Gets stored in the TX FIFO and then extracted by

the hardware and sent to the selected smart card. When the MPU reads this register,

the byte pointer is changed to effectively “read out” the data. Thus, two reads will

always result in an “empty” FIFO condition. The contents of the FIFO registers are not

cleared, but will be overwritten by writes.

STXData.6

STXData.5

STXData.4

STXData.3

STXData.2

STXData.1

STXData.0

SRX Control/Status Register (SRXCtl): 0xFE08

Å

0x00

This register is used to monitor reception of data from the smart card.

Table 81: The SRXCtl Register

MSB

LSB

BIT9DAT – LASTRX

CRCERR

RXFULL

RXEMTY

RXOVRR

PARITYE

Bit Symbol

Function

SRXCtl.7 BIT9DAT

Bit 9 Data – When in sync mode and with MODE9/8B set, this bit will contain

the data on IO (or SIO) pin that was sampled on the ninth CLK (or SCLK) rising

edge. This is used to read data in synchronous 9-bit formats.

SRXCtl.6 –

SRXCtl.5 LASTRX

Last RX Byte – User sets this bit during the reception of the last byte. When

byte is received and this bit is set, logic checks CRC to match 0x1D0F (T=1

mode) or LRC to match 00h (T=1 mode), otherwise a CRC or LRC error is

asserted.

SRXCtl.4 CRCERR (Read only) 1 = CRC (or LRC) error has been detected.

SRXCtl.3

RXFULL (Read only) RX FIFO is full. Status bit to indicate RX FIFO is full.

SRXCtl.2 RXEMTY

(Read only) RX FIFO is empty. This is only a status bit and does not generate

a RX interrupt.

SRXCtl.1 RXOVRR

RX Overrun – (Read Only) Asserted when a receive-over-run condition has

occurred. An over-run is defined as a byte was received from the smart card

when the RX FIFO was full. Invalid data may be in the receive FIFO. Firmware

should take appropriate action. Cleared when read. Additional writes to the

RX FIFO are discarded when a RXOVRR occurs until the overrun condition is

cleared. Will generate RXERR interrupt.

SRXCtl.0 PARITYE

Parity Error – (Read only) 1 = The logic detected a parity error on incoming

data from the smart card. Cleared when read. Will generate RXERR interrupt.

86

Rev.

1.2