TPMC533 User Manual Issue 1.0.1

Page 49 of 107

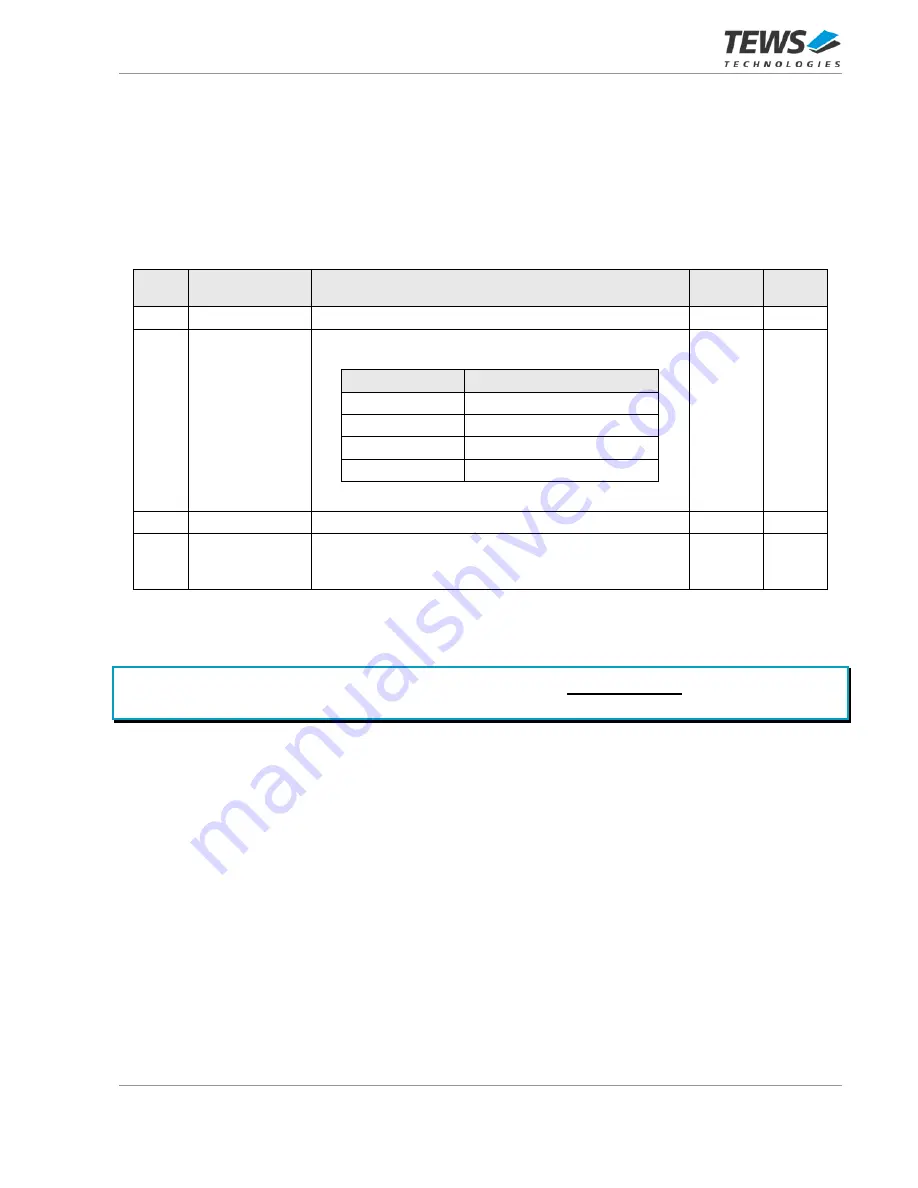

3.2.1.7 Conversion Signals Registers

The following registers are only relevant for ADCs and DACs configured to operate in Sequencer Mode.

3.2.1.7.1

Conversion Clock 1 Generator Register (0x320)

This register determines the frequency of the Conversion Clock 1 Generator output.

Conversion Clock 1 generation is started in the Conversion Signals Generator Enable Register.

Bit

Symbol

Description

Access

Reset

Value

31

-

Reserved

-

-

30:29

CLK1_GEN_SRC

Internal Clock Source

CLK1_GEN_SRC

Internal Clock Source

00

20 MHz

01

22.05 MHz

10

60 MHz

11

Reserved

R/W

00

28

-

Reserved

-

-

27:0

CLK1_GEN_DIV

Clock Divider

These bits set the divider for the selected Internal Clock

Source.

R/W

0xFFF

FFFF

Table 3-50: Conversion Clock 1 Generator Register

The frequency of the Conversion Clock 1 Generator output is:

CLK1_GEN_SRC

CLK1_1