TPMC533 User Manual Issue 1.0.1

Page 62 of 107

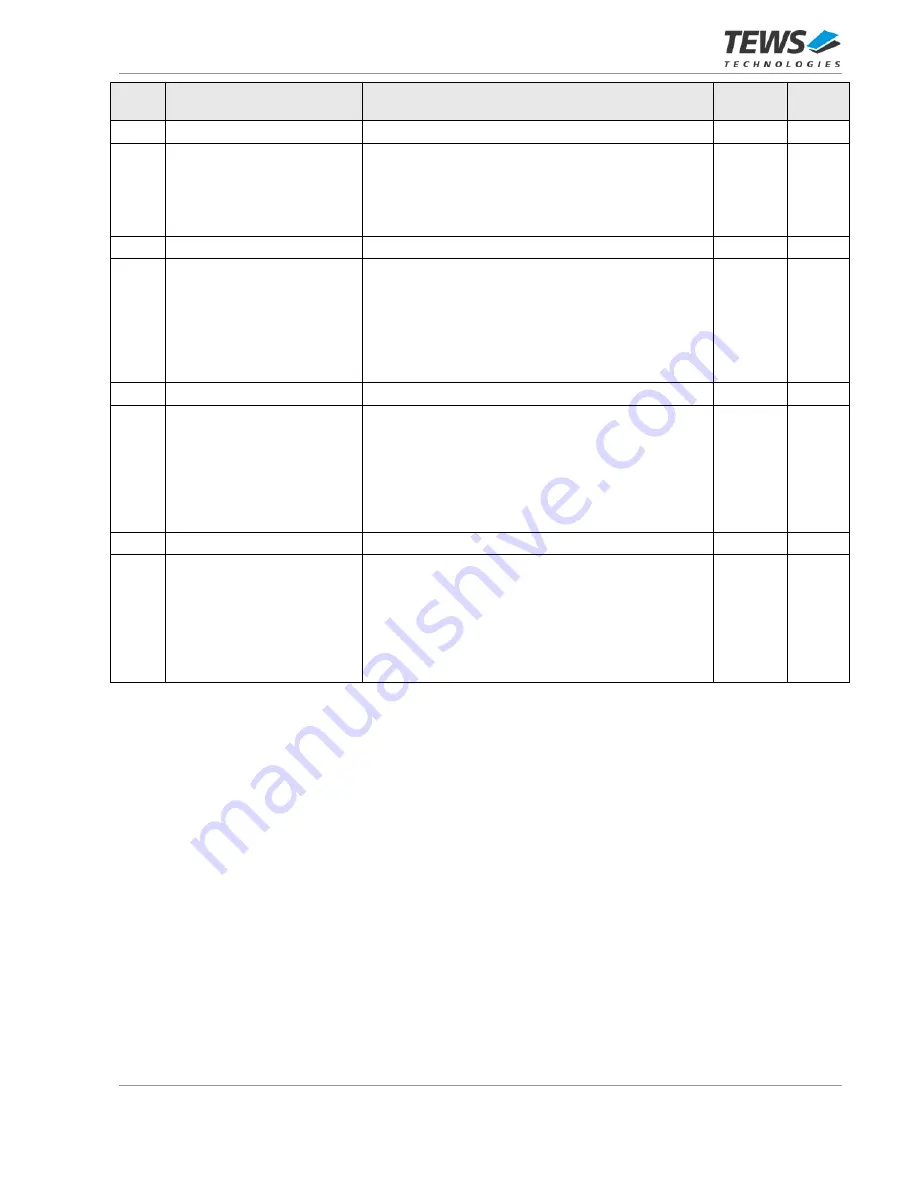

Bit

Symbol

Description

Access

Reset

Value

15:13

-

Reserved

-

-

12

IU_CONV_DONE_IRQ_ENA

Enable IRQ at Input Unit Number of Conversions done

0: disabled

1: enabled

If enabled, an interrupt is asserted when the configured

Number of ADC Conversions have been performed.

R/W

0

11:9

-

Reserved

-

-

8

WR_DMA_TERM_IRQ_ENA

Enable IRQ at ADC Sequencer DMA Buffer Termination

0: disabled

1: enabled

If enabled, an interrupt is asserted when the DMA

Controller of the ADC Sequencer terminates its

provided DMA Buffer. The interrupt status bits indicate

the reason for the termination.

R/W

0

7:5

-

Reserved

-

-

4

OU_CONV_DONE_IRQ_ENA

Enable IRQ at Output Unit Number of Conversions

done

0: disabled

1: enabled

If enabled, an interrupt is asserted when the configured

Number of DAC Conversions have been performed.

For TPMC533-20R: Reserved

R/W

0

3:1

-

Reserved

-

-

0

RD_DMA_TERM_IRQ_ENA

Enable IRQ at DAC Sequencer DMA Buffer Termination

0: disabled

1: enabled

If enabled, an interrupt is asserted when the DMA

Controller of the DAC Sequencer terminates its

provided DMA Buffer.

For TPMC533-20R: Reserved

R/W

0

Table 3-62: Interrupt Enable Register