TPMC533 User Manual Issue 1.0.1

Page 65 of 107

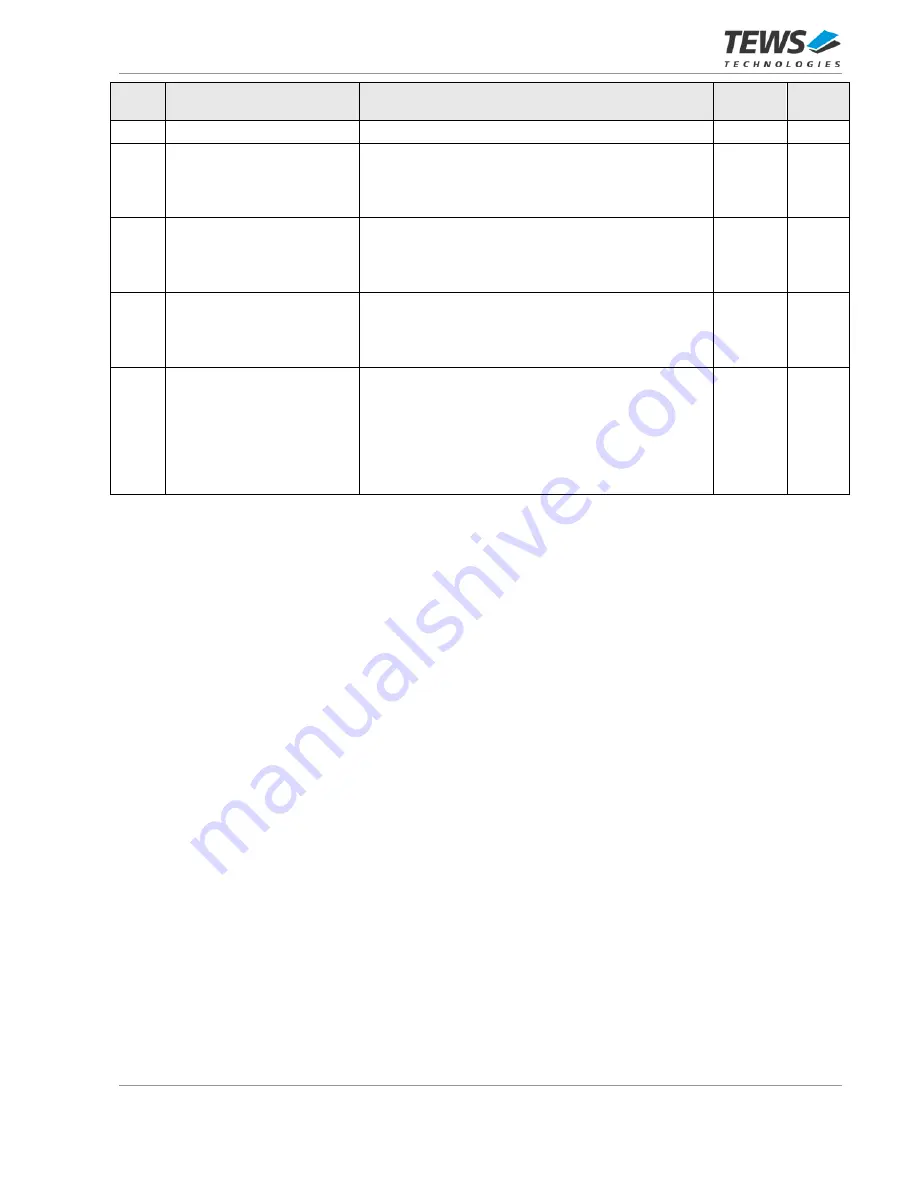

Bit

Symbol

Description

Access

Reset

Value

15:4

-

Reserved

-

-

3

DAC4_ALERT_ENA

Enable IRQ at DAC4 Alert

Refer to the Enable IRQ at DAC1 Alert bit for

description.

For TPMC533-20R: Reserved

R/W

0

2

DAC3_ALERT_ENA

Enable IRQ at DAC3 Alert

Refer to the Enable IRQ at DAC1 Alert bit for

description.

For TPMC533-20R: Reserved

R/W

0

1

DAC2_ALERT_ENA

Enable IRQ at DAC2 Alert

Refer to the Enable IRQ at DAC1 Alert bit for

description.

For TPMC533-20R: Reserved

R/W

0

0

DAC1_ALERT_ENA

Enable IRQ at DAC1 Alert

0: disabled

1: enabled

If enabled, an interrupt is asserted when the DAC1

status is read and any of the over-current bits or the

thermal shutdown bit is set.

For TPMC533-20R: Reserved

R/W

0

Table 3-63: Error Interrupt Enable Register