Basic Test Procedure

29

SLAU579D – June 2014 – Revised August 2018

Copyright © 2014–2018, Texas Instruments Incorporated

ADC3xxxEVM and ADC3xJxxEVM

3.6

ADC32J/34Jxx and TSW14J56 Setup Guide

See the

for more detailed explanations of the TSW14J56 set-up and operation.

This document assumes the HSDC Pro software and the TSW14J56 hardware are installed and

functioning properly.

The ADC32/34xx EVM requires HSDC Pro software version 2.6 or higher with

TSW14J56 hardware of Rev D (or higher).

Single Tone FFT Test

1. The evaluation of the ADC32J/34Jxx EVM requires programming the LMK04828 clock source with the

correct PLL settings to provide a 160 MSPS clock.

•

Connect a USB cable from the ADC32J/34Jxx EVM to the PC.

•

Open the ADC3000 GUI, and connect to the ADC32Jxx or ADC34Jxx EVM.

•

Go to the

Low Level

tab and click

Load Config

.

•

Browse and find the

ADC3xJxx_160MSPS_Operation_LMK_Setting.cfg

.

•

Check that the PLL2 LED D4 is lit – this indicates that the PLL is programmed properly and the

correct clocks are being generated.

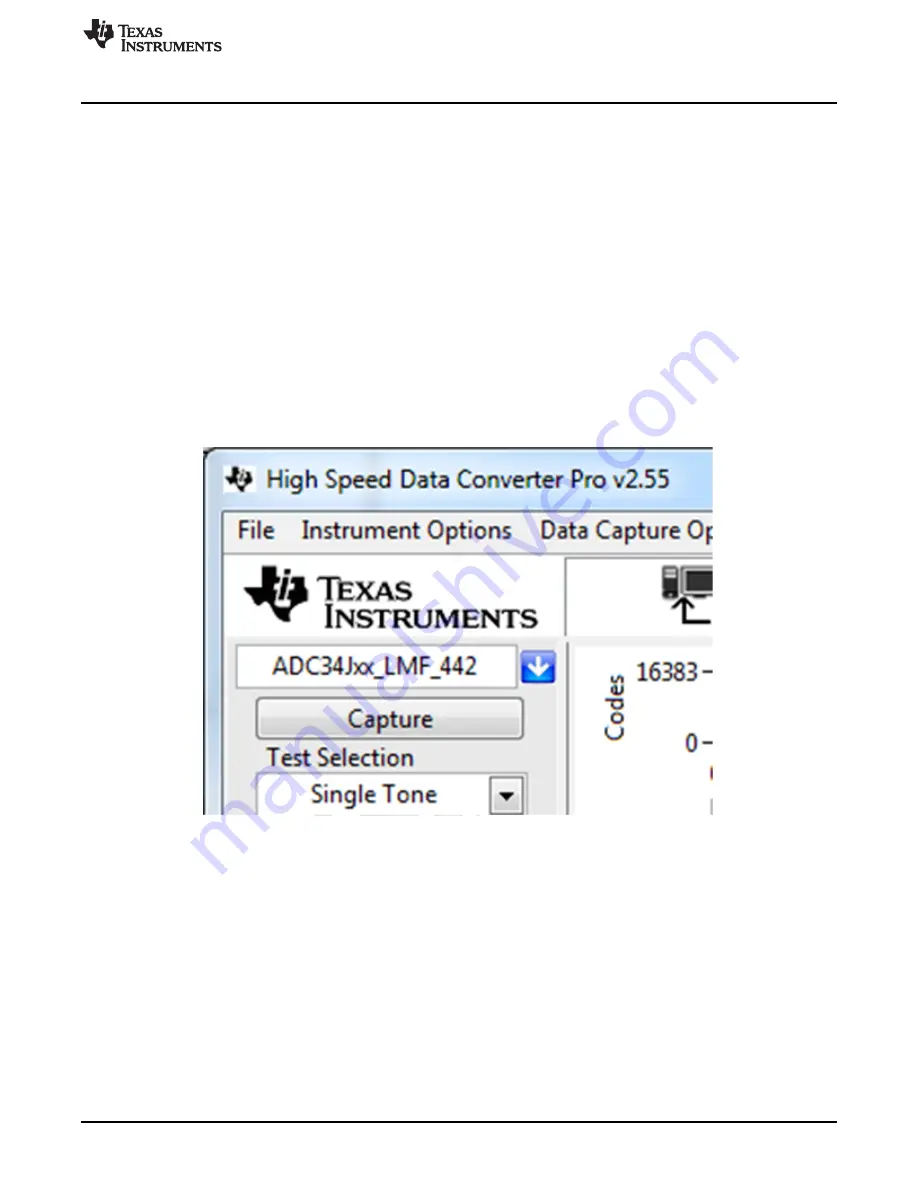

2. Start the HSDC Pro GUI program. When the program starts, select the

ADC

tab and then select

ADC32Jxx_LMF_222

or

ADC34Jxx_LMF_442

device in the

Select ADC

drop-down menu.

Figure 19. Select ADC32Jxx or 34Jxx in the HSDC Pro GUI Program

3. When prompted by

Load ADC Firmware?

, select YES.

4. Select

Single Tone FFT Test

under

Test Selection

.

5. Select the number of sample points (and resulting number of FFT bins) to be used. The example

shown in

has 65536 samples.

6. Enter the ADC32J/34Jxx sampling rate. The example shown in

has the sample rate set at

160 MSPS.

7. Enter the input frequency desired. The example shown in

has the filtered input

frequency set at 10 MHz and around 10 dBm. Adjust to achieve –1 dBFs on the HSDC Pro FFT plot.

8. Select channel 1, 2, 3, or 4 depending on the channel connected to the signal generator.

9. Press the

Capture

button on the HSDC Pro GUI.

10. Observe an FFT result similar to that shown in