Introduction

9

SLAU579D – June 2014 – Revised August 2018

Copyright © 2014–2018, Texas Instruments Incorporated

ADC3xxxEVM and ADC3xJxxEVM

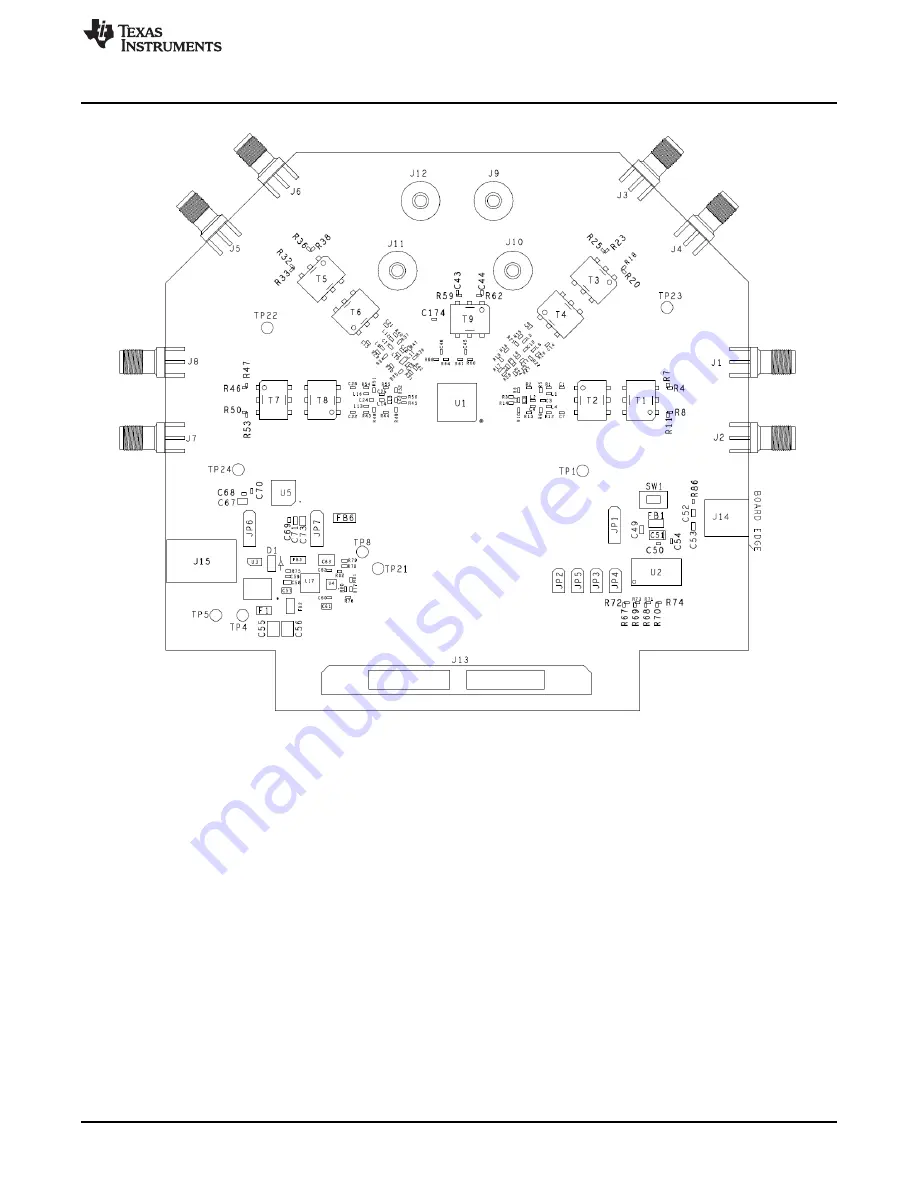

Figure 5. ADC34xx EVM Connector and Jumper Locations

The EVM has a barrel connector for 5-V power. The SMA connectors connect the ADC input and ADC

clock input to the ADC. Typically, the ADC inputs are transformer-coupled to accept single-ended

connections. The input circuit can be configured to connect to two SMA connectors for differential

signaling, if desired.

lists the connector information for the ADC3xxxx.