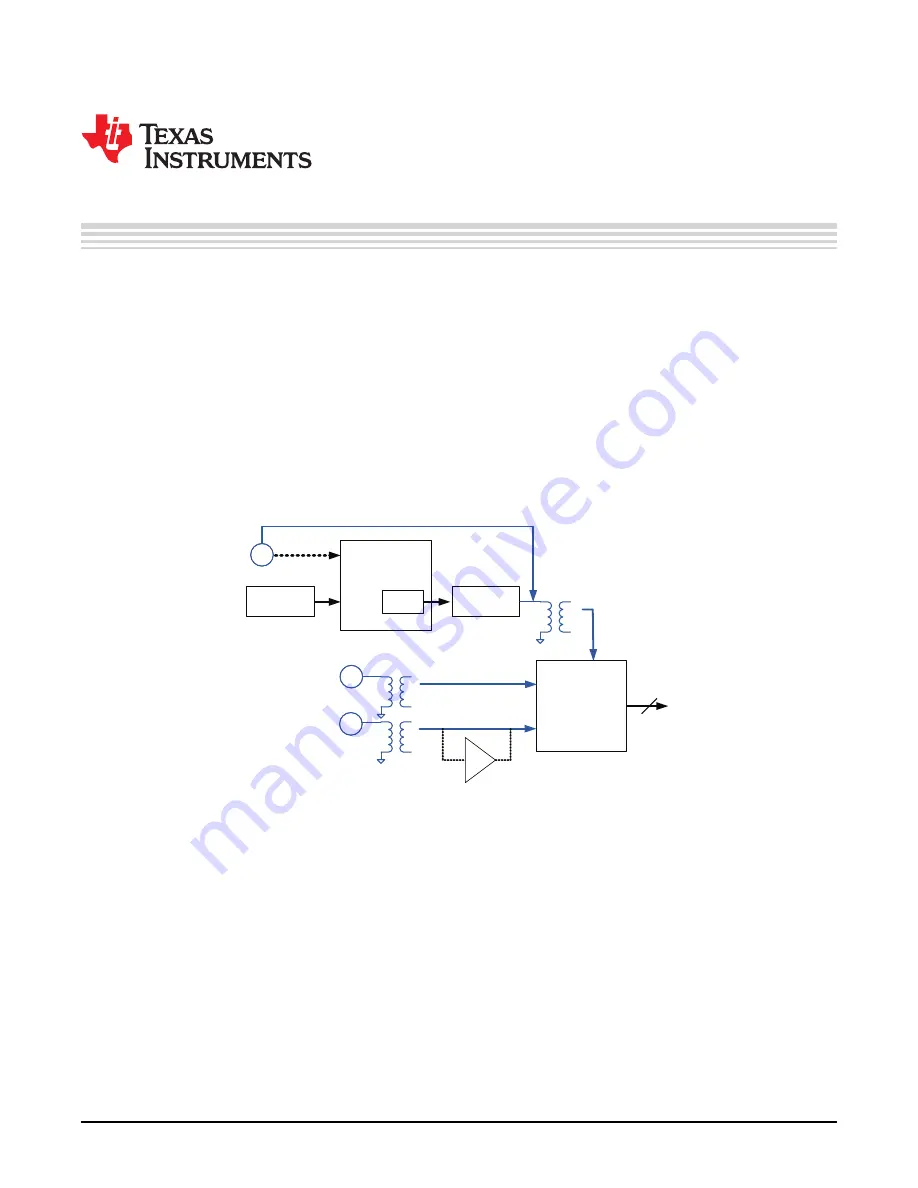

CDCE72010

ADS62Pxx

DATA

Data_CLK

J6

J3

+

_

_

+

J19

VCXO

Divider

245.76MHz

Crystal Filter

+

_

Optional Amplifier Path

Ext. CLK

Ref. CLK

CLK Input

Transformers Coupled

Input Circuit

User's Guide

SLAU237B – May 2008 – Revised July 2010

ADS62PXXEVM

1

Overview

This user’s guide gives a general overview of the evaluation module (EVM) and provides a general

description of the features and functions to be considered while using this module. This manual is

applicable to the ADS62P42/43/44/45/48/49, ADS62P22/23/24/25/28/29 and ADS62C15/17 analog to

digital converters (ADC), which will be collectively referred to as ADS62PXX. This document should be

used in combination with respective ADC data sheet. The ADS62PXX EVM provides a platform for

evaluating the analog-to-digital converter (ADC) under various signal, clock, reference and power supply

conditions.

1.1

EVM Block Diagram

Please refer to

below for EVM block diagram and configuration.

Figure 1. EVM Block Diagram

Windows is a registered trademark of Microsoft Corporation.

5

SLAU237B – May 2008 – Revised July 2010

ADS62PXXEVM

Copyright © 2008–2010, Texas Instruments Incorporated