GND

5 to 36 V

Amp VCC+

J10

J13

J11

J12

JP17

open

TPS5420D

Switching Regulator to 5.3V

TPS7A4501

LDO Regulator to 5V

J

P

1

6

1

J

P

1

9

1

TPS79633

LDO 3.3V

TPS79601

LDO 1.8V

(option for 3.3V)

5 V

Analog

VDD

Digital

VDD

THS4509

TPS79601

LDO 3.3V

TPS79633

LDO 3.3V

To Clock Gen

option, to USB

port

To ADC

To ADC

To Clock

Generator

Option

To Clock

Generator

Option, USB

Port, CMOS

buffer

To USB

Port

Amp VCC-

PWR IN

J17

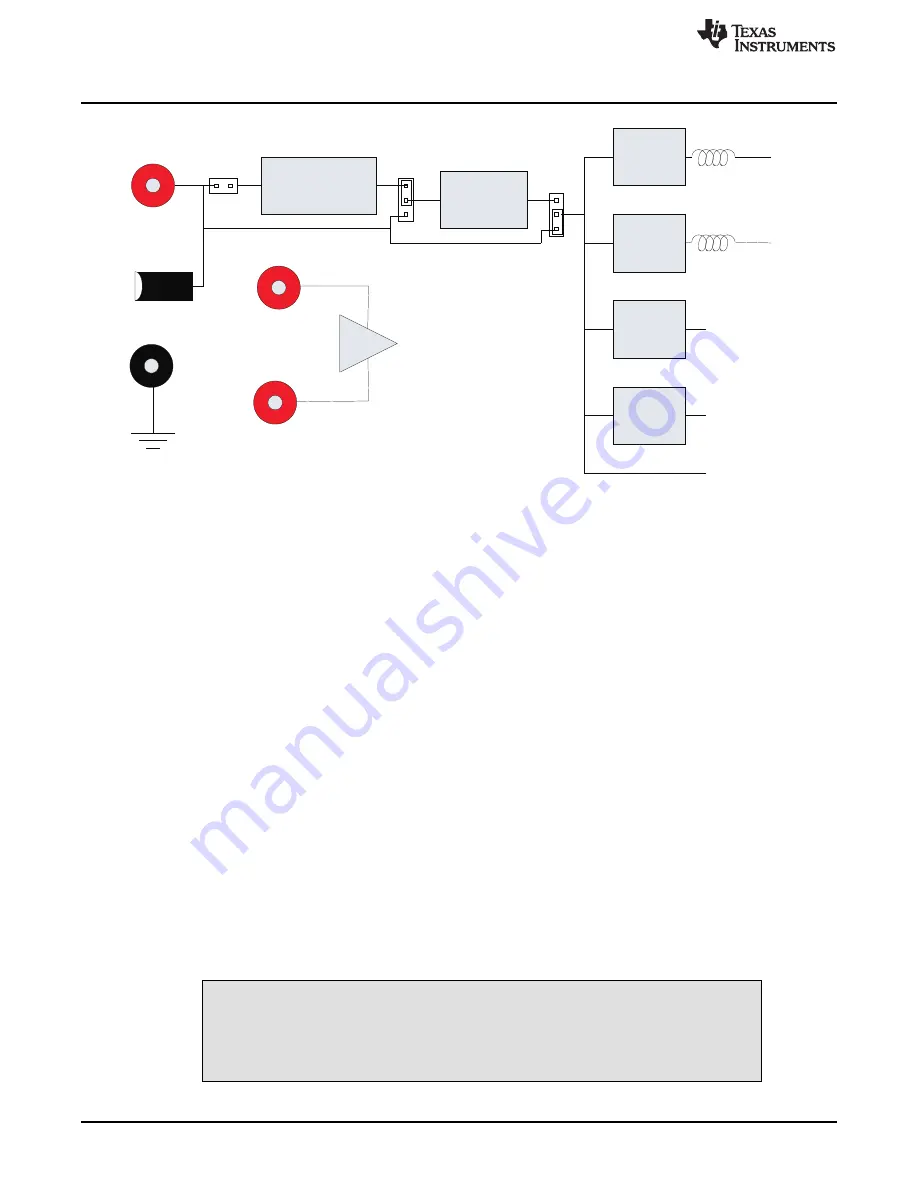

Circuit Description

www.ti.com

Figure 2. ADS62PXXEVM Power Distribution

2.2.2

EVM Power Connections

Power is supplied to the EVM through banana jacks. From this input power, several different ways of

delivering power to the ADC and other EVM functions are available.

shows a simplified

representation of the power options available for the ADS62PXXEVM. The default option is to provide 5V

to J10 or J17, and from there, the EVM generates 3.3V for the analog supply to the ADC and the

necessary digital supply voltage for the populated ADC. The EVM also generates the proper voltages for

optional features of the EVM such as the Clock Generation circuitry, the USB circuitry, and the CMOS

output buffer.

Some ADC devices that may be evaluated on the ADS62PXXEVM platform do not take 1.8V for the digital

supply, but rather require 3.3V for the digital supply. For this reason, an adjustable voltage regulator was

chosen for the digital supply; the output may be changed to 3.3V by changing the value of a resistor, R269

and capacitor C148. The resistor and capacitor need not to be changed in the field unless the ADC is

being changed, because the EVM ships with the correct digital supply voltage for the ADC that is installed.

For reference, ADS62P42/43/44/45,ADS62P22/23/24/25 and ADS62C15 use 3.3V as digital supply for the

ADC whereas ADS62P48/49,ADS62P28/29 and ADS62C17 use 1.8V as digital supply for the ADC.

Power for the optional THS4509 operational amplifier is supplied by banana jacks J11 and J13. If the

amplifier is being evaluated in AC coupled configuration, 5V is supplied to J11, and J13 is connected to

ground. In DC-coupled configuration, 4V is supplied to J11 and –1V is supplied to J13. Otherwise, these

inputs may be left unconnected.

Although various power options are available on this EVM, care must be taken while applying power on

J10 or J17 as different options have different voltage ranges specified.

displays the general

jumper setting information;

displays the various power option settings. Prior to making any jumper

settings, see the schematics located in the design package.

CAUTION

Voltage limits: Exceeding the maximum input voltages can damage EVM

components. Undervoltage can cause improper operation of some or all of the

EVM components.

8

ADS62PXXEVM

SLAU237B – May 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated