1

2

14

15

16

17

23

24

25

26

27

28

29

30

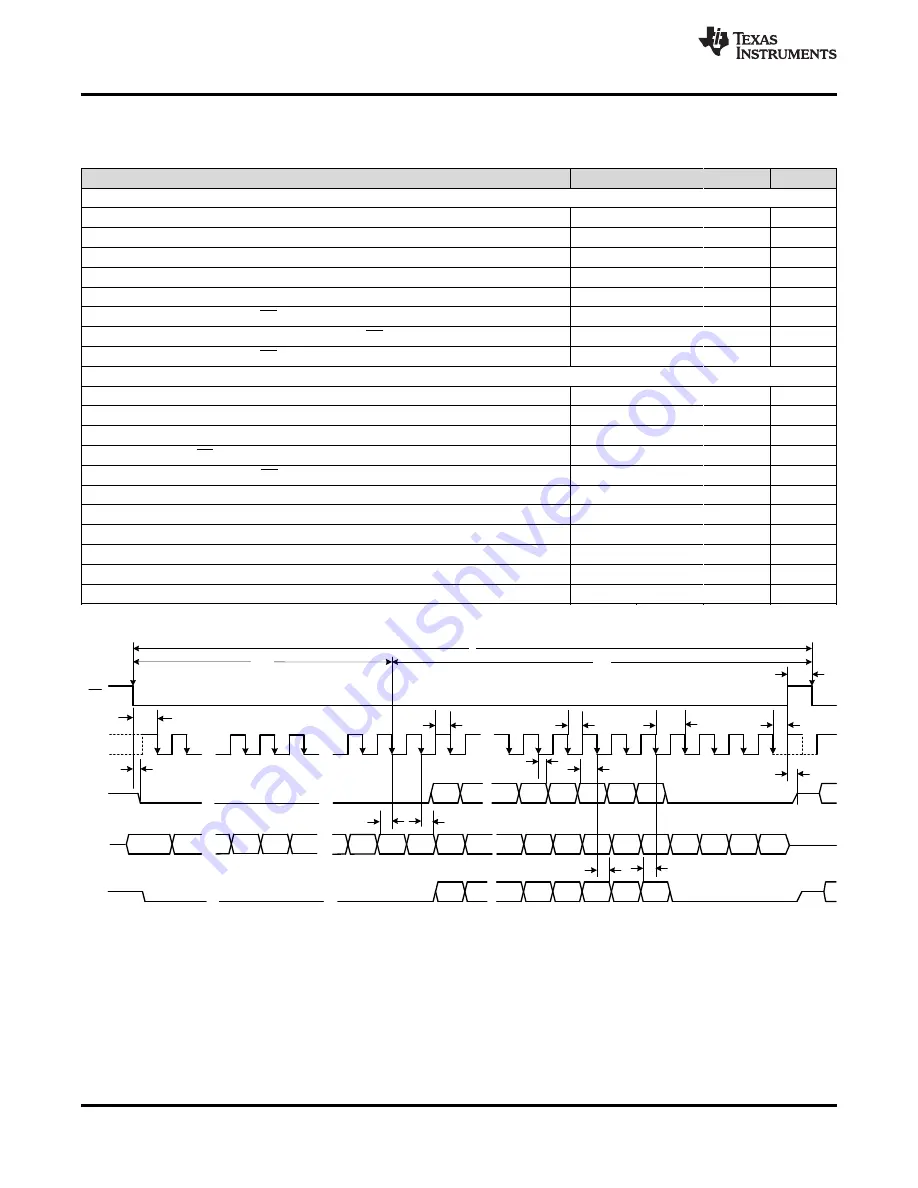

SCLK

CS

D5

#2

D4

#2

D3

#2

D2

#2

D1

#2

D0

#2

SDO

t

SU_CSCK

t

DV_CSDO

t

HT_CKDO

t

SU_DOCK

t

DZ_CSDO

Sample

N

Sample

N + 1

t

ACQ

t

CONV

t

S

Data from sample N

t

PH_CS

31

32

D11

#2

D10

#2

18

B15

B14

B2

B1

B0

X

X

X

X

X

X

SDI

X

X

X

X

X

X

t

PH_CK

t

PL_CK

t

SCLK

t

SU_DICK

t

HT_CKDI

t

D_CKCS

7

8

9

B9

B8

B7

B10

B3

D5

#1

D4

#1

D3

#1

D2

#1

D1

#1

D0

#1

DAISY

D11

#1

D10

#1

t

HT_CKDSY

t

SU_DSYCK

SBAS492 – JULY 2015

7.6 Timing Requirements: Serial Interface

Minimum and maximum specifications are at T

A

= –40°C to 125°C. Typical specifications are at T

A

= 25°C.

AVDD = 5 V, DVDD = 3 V, V

REF

= 4.096 V (internal), SDO load = 20 pF, and f

SAMPLE

= 500 kSPS, unless otherwise noted.

MIN

TYP

MAX

UNIT

TIMING SPECIFICATIONS

f

S

Sampling frequency (f

CLK

= max)

500

kSPS

t

S

ADC cycle time period (f

CLK

= max)

2

µs

f

SCLK

Serial clock frequency (f

S

= max)

17

MHz

t

SCLK

Serial clock time period (f

S

= max)

59

ns

t

CONV

Conversion time

850

ns

t

DZ_CSDO

Delay time: CS falling to data enable

10

ns

t

D_CKCS

Delay time: last SCLK falling to CS rising

10

ns

t

DZ_CSDO

Delay time: CS rising to SDO going to 3-state

10

ns

TIMING REQUIREMENTS

t

ACQ

Acquisition time

1150

ns

t

PH_CK

Clock high time

0.4

0.6

t

SCLK

t

PL_CK

Clock low time

0.4

0.6

t

SCLK

t

PH_CS

CS high time

30

ns

t

SU_CSCK

Setup time: CS falling to SCLK falling

30

ns

t

HT_CKDO

Hold time: SCLK falling to (previous) data valid on SDO

10

ns

t

SU_DOCK

Setup time: SDO data valid to SCLK falling

25

ns

t

SU_DICK

Setup time: SDI data valid to SCLK falling

5

ns

t

HT_CKDI

Hold time: SCLK falling to (previous) data valid on SDI

5

ns

t

SU_DSYCK

Setup time: DAISY data valid to SCLK falling

5

ns

t

HT_CKDSY

Hold time: SCLK falling to (previous) data valid on DAISY

5

ns

Figure 1. Serial Interface Timing Diagram

10

Copyright © 2015, Texas Instruments Incorporated

Product Folder Links: