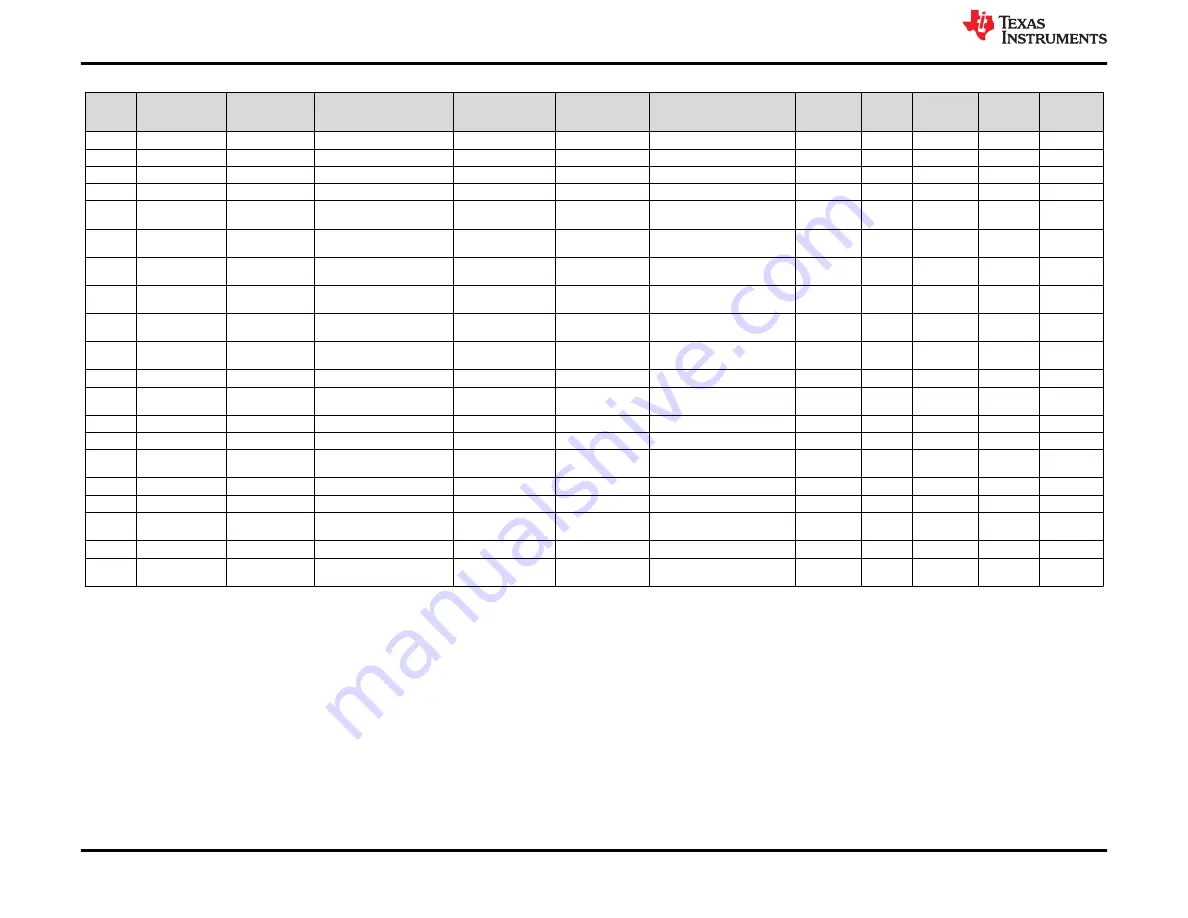

Table 4-6. Pinmux Options for J5/J7 Connector - Site 2

Connecto

r

Pinout

Mode0

Mode1

Mode2

Mode3

Mode4

Mode5

Mode6

Mode7

Mode8

Mode9

Mode10

J5.41

J7.61

J5.42

EXT_REFCLK1

SYNC1_OUT

SPI2_CS3

CLKOUT0

GPIO1_69

J7.62

J5.43

PRG0_PRU0_GPO1

1

PRG0_PRU0_GPI1

1

PRG0_RGMII1_TD0

PRG0_PWM3_TZ_OU

T

GPIO1_11

UART4_RXD

J7.63

PRG1_PRU0_GPO1

9

PRG1_PRU0_GPI1

9

PRG1_IEP0_EDC_SYNC_OUT0

PRG1_PWM0_TZ_OU

T

CPTS0_TS_COMP

TIMER_IO9

GPIO0_64 GPMC0_A2

J5.44

PRG0_PRU0_GPO7 PRG0_PRU0_GPI7 PRG0_IEP0_EDC_LATCH_IN1

PRG0_PWM3_B1

CPTS0_HW2TSPUS

H

CP_GEMAC_CPTS0_HW2TSPUS

H

TIMER_IO6

GPIO1_7

UART4_TXD

J7.64

PRG1_PRU0_GPO1

8

PRG1_PRU0_GPI1

8

PRG1_IEP0_EDC_LATCH_IN0

PRG1_PWM0_TZ_IN

CPTS0_HW1TSPUS

H

TIMER_IO8

GPIO0_63 GPMC0_A1

J5.45

PRG0_PRU0_GPO1

9

PRG0_PRU0_GPI1

9

PRG0_IEP0_EDC_SYNC_OUT0 PRG0_PWM0_TZ_OU

T

CPTS0_TS_COMP

CP_GEMAC_CPTS0_TS_COMP

EHRPWM8_B

GPIO1_19

UART4_RTSn GPMC0_A6

UART3_RXD

J7.65

PRG1_PRU0_GPO1

7

PRG1_PRU0_GPI1

7

PRG1_IEP0_EDC_SYNC_OUT1

PRG1_PWM0_B2

CPTS0_TS_SYNC

TIMER_IO7

GPIO0_62 GPMC0_A0

J5.46

PRG1_PRU0_GPO5 PRG1_PRU0_GPI5

PRG1_PWM3_B2

RGMII1_RX_CTL

GPIO0_50

GPMC0_AD21

J7.66

PRG1_PRU0_GPO7 PRG1_PRU0_GPI7

PRG1_IEP0_EDC_LATCH_IN1

PRG1_PWM3_B1

CPTS0_HW2TSPUS

H

CLKOUT0

TIMER_IO10

GPIO0_52 GPMC0_AD23

J5.47

SPI0_CLK

GPIO1_44

J7.67

PRG0_PRU1_GPO1 PRG0_PRU1_GPI1 PRG0_RGMII2_RD1

GPIO1_21

EQEP0_B

UART5_TXD

J5.48

PRG0_PRU0_GPO6 PRG0_PRU0_GPI6 PRG0_RGMII1_RXC

PRG0_PWM3_A1

GPIO1_6

UART4_CTS

n

J7.68

PRG0_PRU1_GPO2 PRG0_PRU1_GPI2 PRG0_RGMII2_RD2

PRG0_PWM2_A2

GPIO1_22

EQEP0_S

UART5_RTSn

J5.49

I2C0_SCL

UART6_CTSn

GPIO1_64

J7.69

PRG0_PRU1_GPO6 PRG0_PRU1_GPI6 PRG0_RGMII2_RXC

GPIO1_26

EQEP2_A

GPMC0_A19 UART4_CTS

n

J5.50

I2C0_SDA

UART6_RTSn

GPIO1_65

J7.70

PRG0_PRU1_GPO1

1

PRG0_PRU1_GPI1

1

PRG0_RGMII2_TD0

GPIO1_31

EQEP2_I

UART4_RXD

Hardware Description

54

AM243x LaunchPad™ Development Kit User's Guide

SPRUJ12B – AUGUST 2021 – REVISED OCTOBER 2022

Copyright © 2022 Texas Instruments Incorporated