The 48 pin PHY (DP83869) is configured to advertise gigabit operation with the internal delay set to

accommodate the internal delay of the AM243x SoC.

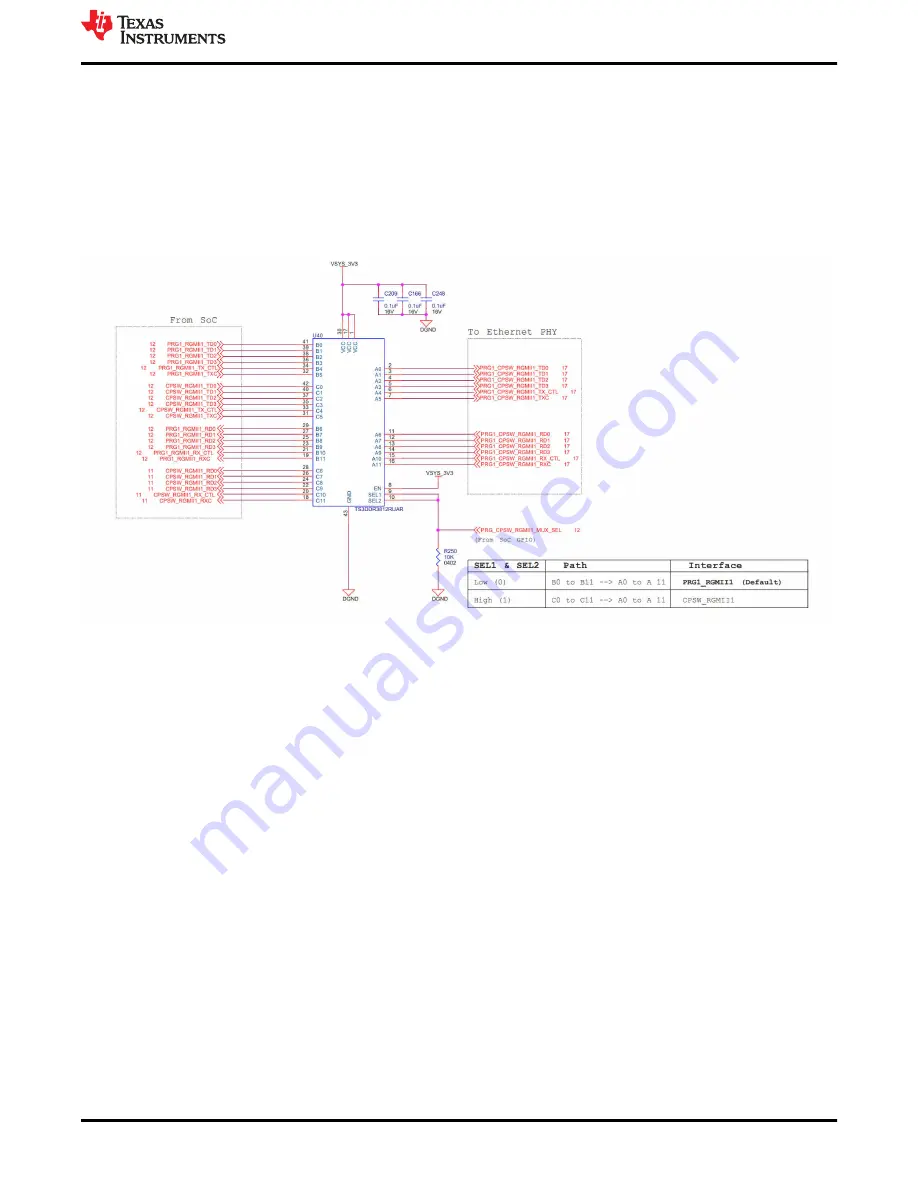

The first PHY is interfaced to the PRG1/CPSW RGMII2 ports of the SoC that are internally multiplexed in the

SoC and the MDI interface from the same PHY is terminated to a RJ45 connector with integrated magnetics.

The second PHY is interfaced to the PRG1/CPSW RGMII1 ports of the SoC that are multiplexed using an

external on-board MUX whose select line is be controlled from a GPIO (PRG_CPSW_RGMII1_MUX_SEL) of the

SoC and the MDI interface from the same PHY is terminated to a RJ45 connector with integrated magnetics. A

1:2 mux (TS3DDR3812RUAR) is used to select between the PRG1 and CPSW RGMII1 ports.

Figure 4-10. CPSW or PRG RGMII1 Ethernet Data Mux

To select between the PRG and CPSW operation for both PHYs, the MDIO and MDC signals, which are

internally multiplexed in the SoC, must be selected from each controller.

Two RJ45 connectors with integrated magnetics and status LEDs (7499111614A from Wurth) are used on the

board for Ethernet 10Mb/100Mb/1Gb connectivity.

4.7.1 Ethernet PHY Strapping

The DP83869 uses many of the functional pins as strap options to place the device into specific modes of

operation. The values of these pins are sampled at power up or hard reset. During software resets, the strap

options are internally reloaded from the values sampled at power up or hard reset. RX_D0 and RX_D1 pins are

4-level strap pins and all other strap pins have two levels.

The Ethernet PHY includes an internal pull-down resistor. The value for the external pull resistors are selected to

provide voltage at the pins of the AM243x as close to ground or 3.3 V as possible.

Address strapping is provided for the RGMII1 PHY and RGMII2 PHY to set the address to 00011 (03h) and 0111

(0Fh), respectively, using strap resistors. Footprint for both pull up and pull down is provided on all the strapping

pins.

Both PHY modes are selected as RGMII to copper with auto-negotiation advertised for 1000 Base-T, 100

Base-Tx, and 10 Base-Te speeds.

Hardware Description

SPRUJ12B – AUGUST 2021 – REVISED OCTOBER 2022

AM243x LaunchPad™ Development Kit User's Guide

65

Copyright © 2022 Texas Instruments Incorporated