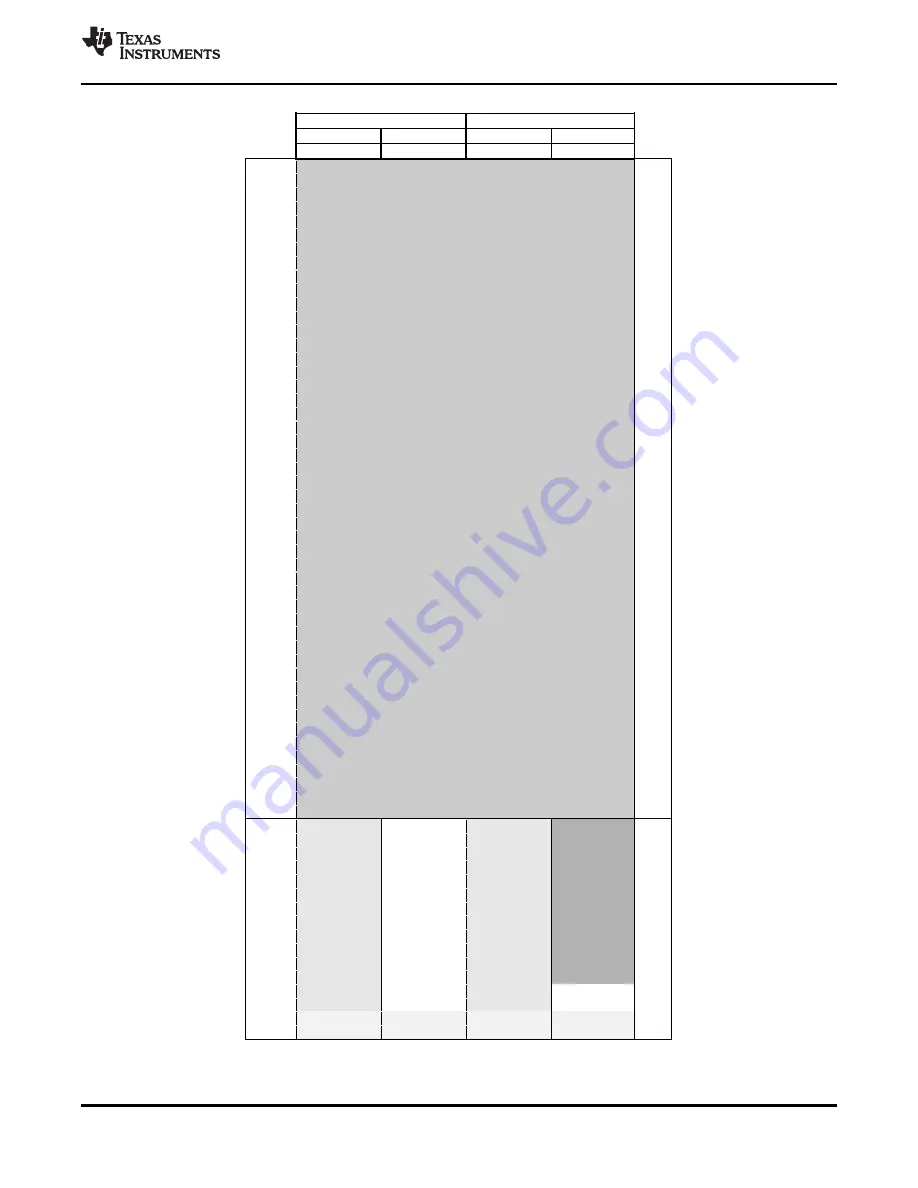

Write

Read

Single byte

Burst

Single byte

Burst

+0x00

+0x40

+0x80

+0xC0

0x00

IOCFG2

R

/W

c

o

n

fi

g

u

ra

ti

o

n

re

g

is

te

rs

,

b

u

rs

t

a

c

c

e

s

s

p

o

s

s

ib

le

0x01

IOCFG1

0x02

IOCFG0

0x03

FIFOTHR

0x04

SYNC1

0x05

SYNC0

0x06

PKTLEN

0x07

PKTCTRL1

0x08

PKTCTRL0

0x09

ADDR

0x0A

CHANNR

0x0B

FSCTRL1

0x0C

FSCTRL0

0x0D

FREQ2

0x0E

FREQ1

0x0F

FREQ0

0x10

MDMCFG4

0x11

MDMCFG3

0x12

MDMCFG2

0x13

MDMCFG1

0x14

MDMCFG0

0x15

DEVIATN

0x16

MCSM2

0x17

MCSM1

0x18

MCSM0

0x19

FOCCFG

0x1A

BSCFG

0x1B

AGCCTRL2

0x1C

AGCCTRL1

0x1D

AGCCTRL0

0x1E

WOREVT1

0x1F

WOREVT0

0x20

WORCTRL

0x21

FREND1

0x22

FREND0

0x23

FSCAL3

0x24

FSCAL2

0x25

FSCAL1

0x26

FSCAL0

0x27

RCCTRL1

0x28

RCCTRL0

0x29

FSTEST

0x2A

PTEST

0x2B

AGCTEST

0x2C

TEST2

0x2D

TEST1

0x2E

TEST0

0x2F

0x30

SRES

SRES

PARTNUM

C

o

m

m

a

n

d

S

tr

o

b

e

s

,

S

ta

tu

s

re

g

is

te

rs

(r

e

a

d

o

n

ly

)

a

n

d

m

u

lt

i

b

y

te

re

g

is

te

rs

0x31

SFSTXON

SFSTXON

VERSION

0x32

SXOFF

SXOFF

FREQEST

0x33

SCAL

SCAL

LQI

0x34

SRX

SRX

RSSI

0x35

STX

STX

MARCSTATE

0x36

SIDLE

SIDLE

WORTIME1

0x37

SAFC

SAFC

WORTIME0

0x38

SWOR

SWOR

PKTSTATUS

0x39

SPWD

SPWD

VCO_VC_DAC

0x3A

SFRX

SFRX

TXBYTES

0x3B

SFTX

SFTX

RXBYTES

0x3C

SWORRST

SWORRST

0x3D

SNOP

SNOP

0x3E

PATABLE

PATABLE

PATABLE

PATABLE

0x3F

TX FIFO

TX FIFO

RX FIFO

RX FIFO

SWRS037B – JANUARY 2006 – REVISED MARCH 2015

Greyed text: not implemented on CC1150 thus only valid for the transceiver version (CC1101)

Figure 5-19. SPI Address Space

Copyright © 2006–2015, Texas Instruments Incorporated

Detailed Description

41

Product Folder Links:

Summary of Contents for CC1150

Page 61: ...PACKAGE OPTION ADDENDUM www ti com 30 May 2018 Addendum Page 2 ...

Page 64: ......

Page 65: ......